# **Design of Nine Level Inverter with Added DC Source using Level Module Technique**

K. Mohan Raj\*, Gorla Narayana Mohan\* and Subhransu Sekhar Dash\*

#### ABSTRACT

A two stage conversion is required to convert high voltage dc to high voltage ac. This process requires very bulky equipment and more complex to control, and becomes less efficient. In Power Distribution System (PDS), DC is replaced by High Frequency AC (HFAC) for better cost and equipment. High Frequency inverter acts as source side inverterin High Frequency AC system. This paper proposes a new level module topology, and it simplifies multilevel inverter circuit. It replaces H-bridge configuration with level module topology. This topology has reduced switches, and also improves efficiency. The topology has an added dc source which allows for an asymmetrical configuration, making it suitable for implementing renewable energy resources. The proposed topology is simulated using MATLAB/ SIMULINK environment. The results are presented to validate the proposed idea.

*Keywords:* Cascaded H-Bridge, Power Distribution System (PDS), High Frequency AC (HFAC). Multi-levelinverter (MLI). Fuel Cells (FC). Diode Clamped Multi level Inverter (DCMLI). Capacitor Clamped Multi level inverter (CCMLI)

## I. INTRODUCTION

Multilevel inverters play an important role in interfacing the local system with the grid. The use of cascade multi-level inverters will help in connecting renewable energy resources with the grid. Asymmetrical MLI has multiple inputs, single output configuration. This helps interface renewable energy with grid.

Most prominent renewable resources such as solar, fuel cells, wind and batteries are available in different voltage levels. Also it is quite important to be grid interactive and for further developments into smart grid.

The conversion process from high voltage dc to ac amplification requires two or more stages, but multi–level inverters make it easy by converting high amplitude dc to ac. But amplification requires more levels. Multi-level inverters make it easy by converting high voltage dc to ac without stepping up and down of voltage levels.

Multi-level Inverter eliminates the use of transformer, and henceforth reducing the losses caused by it. The selection of inverter in dc to ac power conversion is very crucial. Multilevel inverters are used to achieve proper ac output and eliminating harmonics. In high frequency ac power distribution, dc power is being replaced by ac for reduction in cost and bulk equipment [1]. High frequency switching methods are implemented in power distribution systems. Research in hybrid multi-stage inverters with unequal input voltages is being carried out. The switched capacitor network model has been implemented in recent literature [1]. The switched capacitor network uses series and parallel combinations with inverter to achieve a nine level output [2]. Switched capacitor based boost converter is implemented. The multi-level inverter aims to increase voltage of output with switched capacitor and H-bridge inverter at the end [3]. A number of single stage switched capacitor and inductor networks are used in power conversion. The inductors limit peak current in the circuit [4].

SRM University, India, E-mail: mohanraajkumar@gmail.com; narayanamohan.2013@gmail.com; munu\_dash\_2k@yahoo.com

A multi-level inverter with reduced switches is considered. The design is improved byreducing switches. The switching losses are decreased by decreasing number of switches [5]. Various inverter topologies such as Diode Clamped Multi Level Inerter and Capacitor Clamped Multi Level Inerter are studied in [6]-[7]. High frequency power distribution systems require switching at high speeds. The switching speed should support high power for application like hybrid vehicles. The hybrid vehicle with fast switching technique is implemented [8]. Resonant inverters are able to achieve nine level output with phase shifted modulation [9]-[10]. Two stage conversions from dc to ac are done with resonant inverter [11]. Multiple PWM technique is used to reduce harmonic content. The control of the system is also improved by using multiple pwm technique.Some multilevel inverter concepts are discussed in [12]–[16].

Voltage step up converter employs switched capacitor with h-bridge inverter, to obtain ac voltages with varying ratios[17].Neutral point clamped inverter configuration is used for voltage balancing. Different types of neutral point clamped topologies are studied in [18]–[21]. Active filtering techniques are implemented in multi-level inverter for eliminating harmonics [22].High frequency ac power is fed to motor loads in vehicles [23].

Bidirectional power conversion helps save energy and feed energy back to battery [24]. Five level inverter pwm structures are studied with various pwm techniques [25]. Switched capacitor fed multi-level inverter is advantageous in contrast with other multi-level inverter due to multiple input configurations [26]. Series and parallel combination operations reduce switches and eliminate theuse of inductor [27]-[28]. Boost converter fed multi-level inverter has added advantage, such as high amplitude output and also eliminates the use of transformer [29]. Asymmetric configuration is currently researched, since interfacing renewable energy is easily achieved. This available in the recent literature [30]-[33]. A wide range of multi-level inverters and their modulation are discussed in [34]-[39]. Harmonic elimination is done by using various algorithms. The use of filter is also considered in this method, as a way to eliminate harmonics [40]-[41].

#### **II. PROPOSED TOPOLOGY**

Components of multi-level inverters include semiconductor switches, voltage supplies and pwm control. Output voltage and current of MLI are stepped waveforms. Multi-level inverter can be implemented from basic three-level and is continued up to 'n' level multi-level inverter. Mostly used multi-level inverters in recent years are the Neutral Point Clamped multi-level inverter(NPC), Flying Capacitor multi-level inverter (FC) and Cascaded H-Bridge multi-level inverter (CHB). The neutral point in NPC balances the voltage in the dc link and provides balanced voltage to the inverter.

The flying capacitor technique uses capacitor and diodes to balance and split the voltage equally across the circuit to provide balanced voltage to inverter and reduce damage on switches. The usage of many inputs makes cascaded H-bridge more preferable than other inverters. The H-bridge has multiple inputs and still produces the same output as other topologies.

It combines inputs with varying voltage levels together. Single stepped wave output is achieved. The need to incorporate multiple inputs into a single output is increasing. So hybrid asymmetric multi-stage topologies are becoming more prevalent area in research. In the asymmetric configurations, the voltage inputs vary in number and magnitude of dc voltage supplies are unequal.

Cost reducing topologies are considered in improving inverter without compromising on reliability and efficiency. Reducing switches by changing the design of the inverter seems plausible. Incorporating multiplevoltage inputs is important. Such hybrid multi-stage topology is designed. This topology has multi-level configuration and an added dc voltage supply.

#### **III. LEVEL MODULE TOPOLOGY**

A new level module topology is proposed for reducing the number of semiconductor switches and still obtains the same nine level output. This is done by an added dc source. The topology is designed in such a

way that we can obtain the required voltage by switching on devices. Two switches operate to produce output level using single source at one instant and two sources at other instant. This helps us to replace switched capacitor network which is complex and difficult to control.

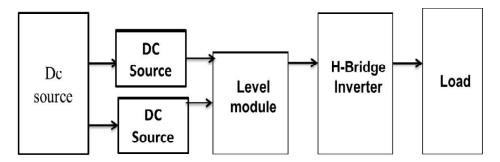

# **IV. BLOCK DIAGRAM OF LEVEL MODULE TOPOLOGY**

The block diagram shows an added dc source with respect to symmetrical configuration. The level module consists of 5 switches. The level module connects the three dc sources with h-bridge.

Figure 1: Block diagram of level module topology

The added dc source is an advantage in this configuration. The input voltage levels are having the ratio of 1:2:4. The level module utilizes these sources by proper switching pattern. The h-bridge connects level module to the load.

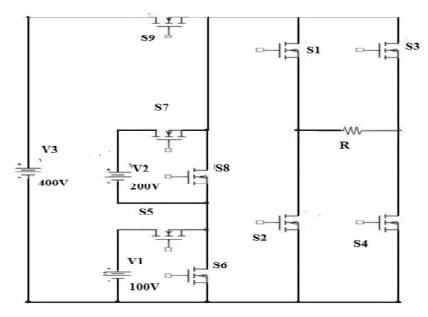

# V. CIRCUIT DIAGRAM

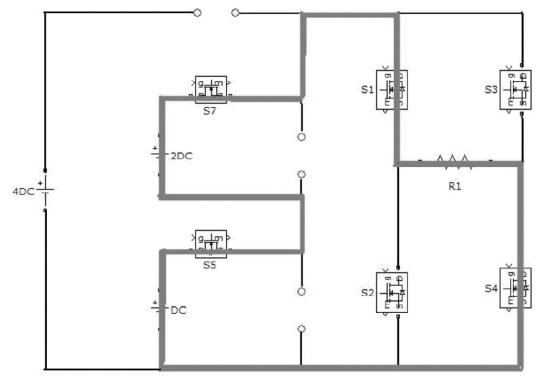

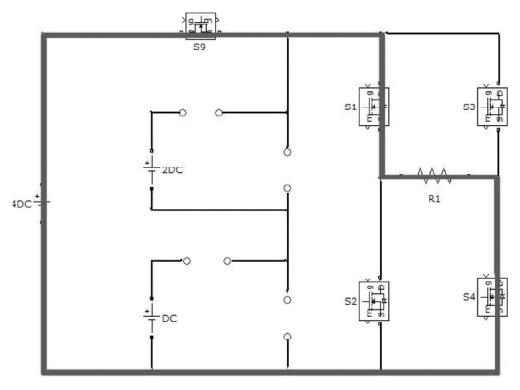

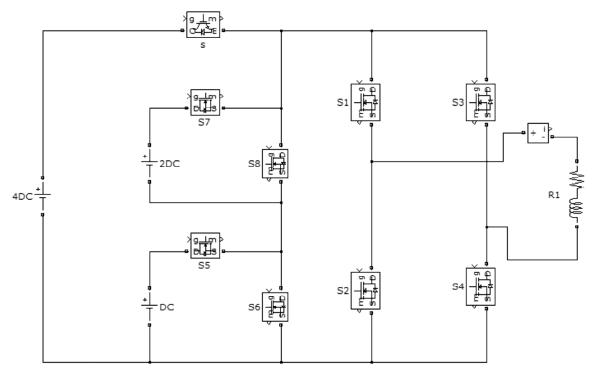

The level module circuit has 5 switches. These switches are operated by pulse generator circuit. The hbridge has four switches; first diagonal switches operate to give positive half of output while the other pair operates during negative half. The sources are switched on at frequent intervals.

The conventional system has 12 switches and 2 dc sources with complex control circuit.But this design reduces the switches to 9. It also has an added source. The 5 switches reduces switching loss and total power loss. The complex control is also simplified from phase shifted modulation to a pulse generator

Figure 2: Circuit diagram of level module topology

circuit. The asymmetrical configuration will be very useful in interfacing unequal inputs with single load and the system is also effective against voltage unbalancing.

#### **VI. FOURIER ANALYSIS**

The harmonic content in the output voltage can be determined by using Fourier series.

It is the method of defining a periodic waveform in terms of trigonometric function.

$$V_{O=a_0+\sum_{n=1}^{\infty}(a_n\cos(n\,\omega t)+b_n\sin(n\,\omega t))}\tag{1}$$

Since is  $V_0(t)$  an odd function,  $a_n=0$  and  $b_n$  is given by

$$b_n = \int_0^T V_0(t) \sin(n\omega t) \tag{2}$$

The total harmonic distortion is a measure of harmonic distortion present in inverter output.

The total harmonic distortion is given by

$$THD = \sqrt{\frac{\sum_{n=2}^{\infty} V_n^2}{V_1^2}}$$

(3)

Where Vn is the nth harmonic voltage and  $V_1$  is the fundamental voltage.

#### **VII. MODES OF OPERATION**

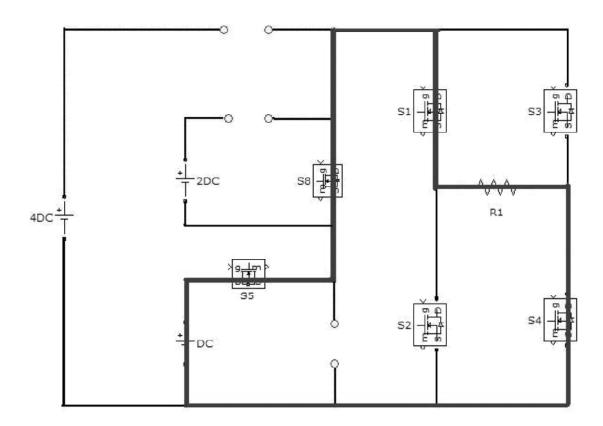

There are five modes of operation. During zero state, no switch conducts also the absence of capacitor and inductor means no free-wheeling mode.

Figure 3(a): Mode 1 equivalent circuit

The switches S5 and S8 are ON to produce  $1V_{dc}$  at output. The other source side switches S6, S7 and S9 are in OFF state condition. The switches S1 and S4 are ON state and produce positive half of H-bridge. During mode 2 switches S6 and S7 conduct with S1 and S4 for positive mode. S2 and S3 switches conduct during negative mode of operation.

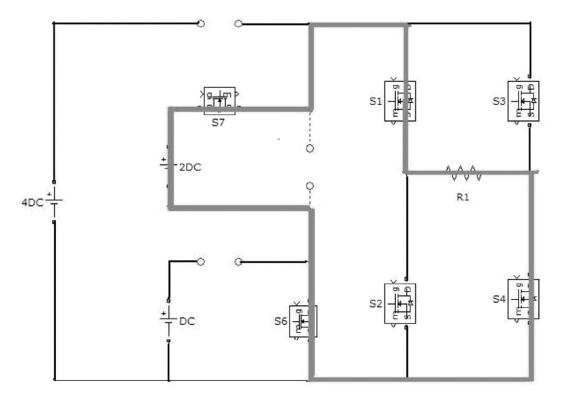

Figure 3(b): Mode 2 equivalent circuit

Figure 3(c): Mode 3 equivalent circuit

Figure 3(d): Mode 4 equivalent circuit

During Mode 3, the voltage sources V1 and V2 are switched ON by S5 and S7. The other switches are turned off. During the fourth mode of conduction the switch S9 conducts and all other switches are off. The output obtained across RL load is  $4V_{dr}$ .

# **VIII. SIMULATIONAND RESULTS**

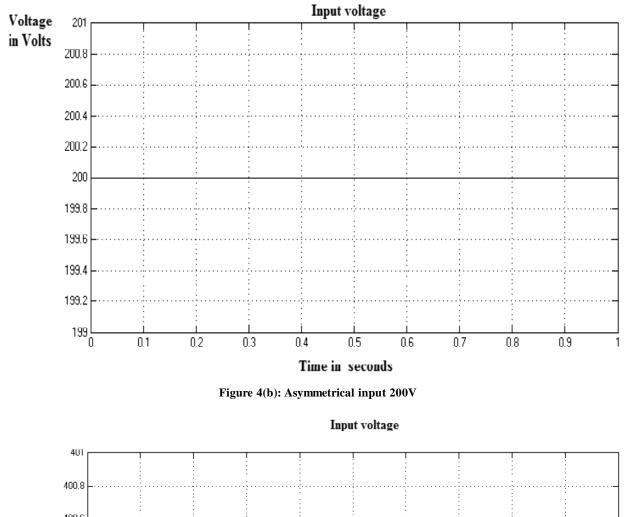

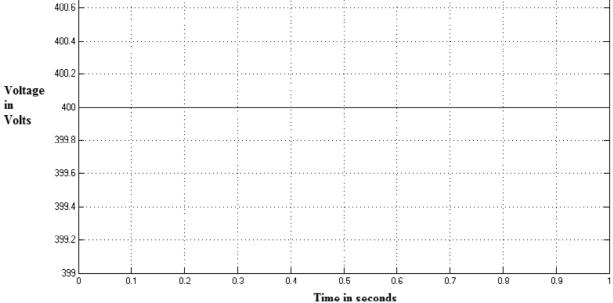

The circuit model is implemented in Matlab environment and simulated. The input voltages are having the ratio of 1:2:4 are 100V, 200V and 400V. The output is taken across the RL load.

Time in seconds

Figure 4(c): Asymmetrical input 400V

The asymmetrical configuration allows input voltages in the ratio of 1: 2: 4. To obtain output voltage as 250V, the input voltages can be given as 25V, 50V, 100V.

Figure 5: Simulation of inverter with RL load

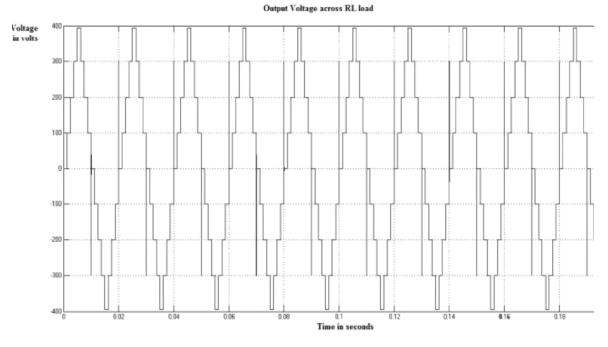

The output taken across RL load is nine level stepped wave output.

#### Figure 6: Output voltage across RL load

Thee voltage spikes occur whenever voltage rises 0 to  $1V_{dc}$ . The output can be obtained as 230V which can be obtained by flexible input 50V, 100V and 200V. The nine level output obtained across the motor has peak to peak voltage of 800V.

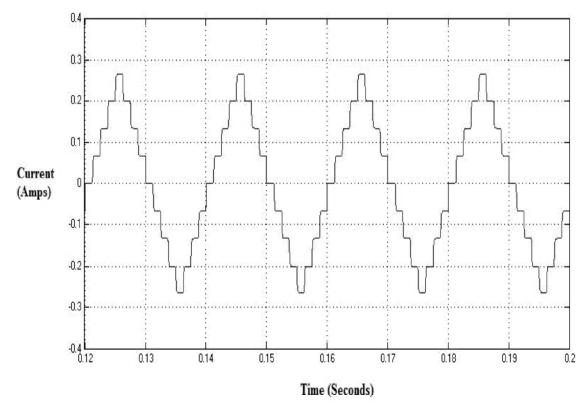

Figure 7: Output current across RL load

The current output is a stepped waveform obtained across RL load. The peak to peak current is 5Amps.

A single phase asynchronous motor (capacitor start) is used. The output is taken across the motor.

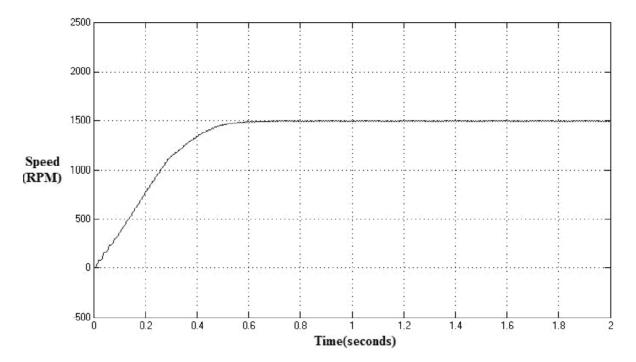

The motor starts slowly and quickly picks up speed. The motor reaches 1500RPM and continues at same speed. The motor speed can't be controlled as that being a disadvantage. But this drive is excellent choice for constant speed and torque applications.

Figure 8: Speed characteristics of the single phase asynchronous motor

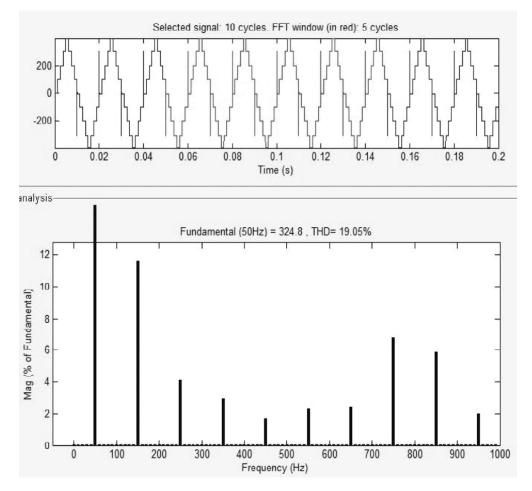

Figure 9: FFT analysis for total harmonic distortion

The total harmonic distortion analysis is obtained by Fast Fourier transform tool in Matlab software. The THD is measured to be 19.05%. The cascaded multi-level inverter can be used as a comparison with this inverter.

A comparison of symmetrical nine level mli and improved level module technique is done. The parameters such as number of switches, THD, Fundamental component and third harmonic are used to compare both the inverters. The switches are reduced and the harmonic levels remain the same for both topologies. The result obtained is nearer to previous topology. The 5<sup>th</sup> and 7<sup>th</sup> harmonic content are also similar. This topology incorporates more voltages and reduces the switches to achieve the similar output. The FFT shown in figure. 8 shows the selected waveform, fundamental component.

.....

| S.No. |                          | symmetrical 9-level MLI and level module topology<br>Comparison of symmetrical 9 level and<br>level module topology |                      |

|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|

|       | Parameters               | Symmetrical 9 level mli                                                                                             | Level moduletopology |

| ι.    | No. of Switches          | 12                                                                                                                  | 9                    |

| 2.    | Fundamental              | 323.7                                                                                                               | 324.8                |

| 3.    | Thd                      | 18.18%                                                                                                              | 19.05%               |

| 1.    | 3 <sup>rd</sup> harmonic | 11.71                                                                                                               | 11.59                |

# **IX. CONCLUSION**

In this paper, a new level module topology is proposed for an application where dc to ac power conversion takes place with asymmetrical source such as batteries, fuel cells, and renewable energy sources. The new level module topology is designed with lesser switches and added dc source. The voltage and current waveforms are obtained, and show stepped wave peak to peak output.

The proposed inverter with modes of operation, simulation, THD analysis and comparison with conventional system is done. The pwm pulses are generated based on the requirement of the inverter switches. The results obtained show similar performance even by changing design and reducing switches.

### REFERENCES

- [1] Junfeng Liu, K.W.E Cheng and Yuanmao Ye, "A Cascaded Multilevel Inverter based Switched-Capacitor for High-Frequency AC Power Distribution System," IEEE Trans on Power Electron., vol. 29, no. 8, 4219-4230, Aug. 2014.

- [2] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

- [3] Marco S. W. Chan and K. T. Chau, "A New Switched-Capacitor Boost Multilevel Inverter using Partial Charging," IEEE Trans. Circuits and Systems, vol. 54, no. 12, 1145-1149, Dec. 2007.

- [4] Y. Yuanmao and K. W. E. Cheng, "A family of single-stage switched capacitor–inductor PWM converters," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5196–5205, Nov. 2013.

- [5] Ammar Masaoud, Hew Wooi Ping, Saad Mekhilef and Ayoub SulimanTallah, "New Three- Phase Multilevel Inverter with Reduced Number of Power electronic Components," IEEE Trans. Power Electron., vol. 29, no. 11, 6018-6029, Nov. 2014.

- [6] On-cheongMak and Adrian Ioinovici, "Switched-Capacitor Inverter with High Power Density and Enhanced Regulation Capability," IEEE Trans. Fundamental Theory and Appl. vol. 45, no. 4, 336-347, Apr. 1998.

- [7] I. Colak*et al.*, "Review of multilevel voltage source inverter topologies and control schemes," *Energy Convers. Manage.*, vol. 52, pp. 1114–1128, 2011.

- [8] P. Jain and H. Pinheiro, "Hybrid high frequency AC power distribution architecture for telecommunication systems," *IEEE Trans. Aerospace Electron. Syst.*, vol. 35, no. 1, pp. 138–147, Jan. 1999.

- [9] J. Rodriguez *et al.*, "Multilevel converters: An enabling technology for high-power applications," *Proc. IEEE*, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

- [10] Y. Zhongming, P. K. Jain, and P. C. Sen, "A full-bridge resonant inverter with modified phase-shift modulation for highfrequency AC power distribution systems," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2831–2845, Oct. 2007.

- [11] Z.Ye, P. K. Jain, and P. C. Sen, "A two-stage resonant inverter with control of the phase angle and magnitude of the output voltage," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2797–2812, Oct. 2007.

- [12] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel PWM methods at low modulation indices," *IEEE Trans. Power Electron.*, vol. 15, no. 4, pp. 719–725, Jul. 2000.

- [13] P. P. Rodriguez, M. M. D. Bellar, R. R. S. Munoz<sup>-</sup>Aguilar, S. S. Busquets-Monge, and F. F. Blaabjerg, "Multilevel clamped multilevel converters (MLC)," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1055–1060, Mar. 2012

- [14] K. Ilves, A. Antonopoulos, S. Norrga, and H.-.P. Nee, "A new modulation method for the modular multilevel converter allowing fundamental switching frequency," *IEEE Trans. Power Electron.*, vol. 27, no. 8, 3482–3494, Aug. 2012.

- [15] H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter (MMCC)," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3119–3130, Nov. 2011.

- [16] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," *IEEE Trans. PowerElectron.*, vol. 28, no. 2, pp. 625–636, Feb. 2013

- [17] K. K. Law, K. W. E. Cheng, and Y. P. B. Yeung, "Design and analysis of switched-capacitor based step-up resonant converters," *IEEE Trans. Circuit Syst. I, Reg. Papers*, vol. 52, no. 4, pp. 943–948, Apr. 2005.

- [18] J. Rodriguez et al., "A survey on neutral-point-clamped inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2219– 2230, Jul. 2010.

- [19] Z. Li *et al.*, "A family of neutral point clamped full-bridge topologies for transformer less photovoltaic grid-tied inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 730–739, Feb. 2013.

- [20] L. Jun *et al.*, "A new nine-level active NPC (ANPC) converter for grid connection of large wind turbines for distributed generation," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 961–972, Mar. 2011.

- [21] W. Yong and W. Fei, "Novel three-phase three-level-stacked neutral point clamped grid-tied solar inverter with a split phase controller," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2856–2866, Jun. 2013.

- [22] S. Chakraborty and M. G. Simoes, "Experimental evaluation of active filtering in a single-phase high-frequency AC micro grid," IEEE Trans .Energy Convers., vol. 24, no. 3, pp. 673–682, Sep. 2009.

- [23] C. C. Antaloae, J. Marco, and N. D. Vaughan, "Feasibility of high frequency alternating current power for motor auxiliary loads in vehicles," IEEE Trans. Veh. Technol., vol. 60, no. 2, pp. 390–405, Feb. 2011.

- [24] H. L. Chan, K. W. E. Cheng, and D. Sutanto, "Bidirectional phase-shifted DC–DC converter," *IEEE Electron. Lett.*, vol. 35, no. 7, pp. 523–524, Apr. 1999.

- [25] S.-J. Park, F.-S. Kang, M. H. Lee, and C.-U. Kim, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEETrans. Power Electron.*, vol. 18, no. 3, pp. 831–843, May 2003.

- [26] B. Axelrod, Y. Berkovich, and A. Ioinovici, "A cascade boost-switched-capacitor-converter—Two level inverter with an optimized multilevel out-put waveform," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 52, no. 12, 763–2770, Dec. 2005.

- [27] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel DC voltage sources," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

- [28] Y. Hinago and H. Koizumi, "A switched-capacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878–887, Feb. 2012.

- [29] M. S. W. Chan and K. T. Chau, "A new switched-capacitor boost-multilevel inverter using partial charging," *IEEE Trans. Circuits Syst.II: Exp. Briefs*, vol. 54, no. 12, pp. 1145–1149, Dec. 2007.

- [30] K. K. Law and K. W. E. Cheng, "Examination of the frequency modulation and lifting techniques for the generalized power factor correction switched-capacitor resonant converter," *Int. J. Circuit Theory Appl.*, vol. 36, no. 7, pp. 839–855, Oct. 2008.

- [31] K. Ding, K. W. E. Cheng, and Y. P. Zou, "Analysis of an asymmetric modulation method for cascaded multilevel inverters," *IET Power Electron.*, vol. 5, no. 1, pp. 74–85, Jan. 2012.

- [32] A. Ioinovici, "Switched-capacitor power electronics circuits," *IEEE Circuits Syst. Mag.*, vol. 1, no. 1, pp. 37–42, Jan. 2001.

- [33] L. G. Franquelo *et al.*, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [34] Rodriguez *et al.*, "Multilevel converters: An enabling technology for high-power applications," *Proc. IEEE*, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

- [35] S. Gui-Jia, "Multilevel DC-link inverter," IEEE Trans. Ind. Appl., vol. 41, no. 3, pp. 848–854, May/Jun. 2005.

- [36] P. Fang Zheng, "A generalized multilevel inverter topology with self-voltage balancing," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611–618, Mar./Apr. 2001.

- [37] K. Ilves*et al.*, "A new modulation method for the modular multilevel converter allowing fundamental switching frequency," *IEEE trans. Power Electron*, vol. 27, no. 8, pp. 3482–3494, Aug. 2012.

- [38] S. Suroso and T. Noguchi, "Multilevel current waveform generation using inductor cells and H-bridge current-source inverter," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1090–1098, Mar. 2012.

- [39] C. Govindaraju and K. Baskaran, "Efficient sequential switching hybrid modulation techniques for cascaded multilevel inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1639–1648, Jun.2011.

- [40] D. Zhong, L. M. Tolbert, and J. N. Chiasson, "Active harmonic elimination for multilevel converters," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 459–469, Mar. 2006.

- [41] A. Kavousi, B. Vahidi, R. Salehi, M. Bakhshizadeh, N. Farokhnia, and S. S. Fathi, "Application of the Bee algorithm for selective harmonic elimination strategy in multilevel inverters," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1689– 1696, Apr. 2012.