# Regulation of Power Flow by Advanced Unified Power Flow Controller

K. Manoz Kumar Reddy<sup>1</sup>, Dr A.Kailasa Rao<sup>2</sup> and Dr R. Srinivas Rao<sup>3</sup>

<sup>1</sup>Associate Professor, EEE Department, Sriaditya Engineering College, Surampalem, AP,

<sup>2</sup>Professor, Pragati Engineering College, Surampalem, AP

<sup>3</sup>Professor, JNT University, Kakinada, AP

Email:- hodeee@sriaditya.edu.in

#### ABSTRACT

The performance of advanced unified power flow controller in controlling the flow of active power and reactive power of buses and lines and voltage profile of the bus is the main focus in this paper. The behaviour of UPFC is studied by using its voltage source model. For load flow analysis this model is incorporated in Fast Decoupled load flow algorithm. UPFC and the power balance equations of network are combined into single set of non-linear algebraic equations and solved according to the Fast Decoupled load flow algorithm. Case study is carried on standard 5 bus network and performance of UPFC is checked by using MATLAB. The results of network in terms of active and reactive power flows in the bus and in the line and similarly voltage profile at the bus with and without UPFC are compared.

**Keywords:** Active power, Reactive power, Fast Decoupled algorithm, Unified power flow controller, Voltage source model

# **1. INTRODUCTION**

With increasing demand of electric power, the existing transmission networks even in the developed countries are found to be weak which results in a poor quality of unreliable supply. In order to expand or enhance the power transfer capability of existing transmission network the concepts of FACTS (Flexible AC transmission system) is developed by the Electric Power Research Institute (EPRI) in the late 1980s. The main objective of facts devices is to replace the existing slow acting mechanical controls required to react to the changing system conditions by rather fast acting FACTs means alternating current transmissions systems electronic controls. incorporating power electronic based and other static controllers to enhance controllability and increase power transfer capability [1-2]. Facts controllers may be series, shunt or combination of both. Shunt controllers inject current into the system and may be variable impedance or variable source or both for ex: Static Synchronous Compensator (STATCOM), static var compensator (SVC) etc. Series controllers inject voltage in series with the line for ex: Static Synchronous Series Compensator (SSSC), Thyristor controlled Series Capacitor (TCSC), Thyristor switched series Capacitor (TSSC), Thyristor Controlled Series Reactor (TCSR), Thyristor Switched Series Reactor

(TSSR). A combination of static synchronous compensator (STATCOM) and static series compensator (SSSC) which are coupled via a common dc link to allow bidirectional flow of real power between series o/p terminals of SSSC and shunt o/p terminals of STATCOM is called UPFC (unified Power Flow Controller).

Among different kinds of FACTS devices the UPFC is the most versatile and effective device which was introduced in 1991. The UPFC consist of voltage source converters, one connected in series and other in shunt and both are connected back to back through a D.C capacitor [3-5]. In order to investigate the impact of UPFC on power systems effectively, it is essential to formulate their correct and appropriate model. In the area of power flow analysis models of UPFC have been published which treat the UPFC either as one series voltage source and one series current source model or both the series and the shunt are represented by voltage sources [6-8].

In this paper voltage source model of UPFC is incorporated in Fast Decoupled algorithm in order to observe the control of power flow and also to regulate the voltage in electrical power transmission systems. Generally for transmission systems active power changes are less sensitive to changes in voltage magnitude and are most sensitive to changes in phase angle. Similarly reactive power is less sensitive to changes in angle and mainly dependent on changes in voltage magnitude. Hence, Fast Decoupled load flow algorithm which requires less time per iteration is used in this paper.

Generally there are two methods of solving the load flow equations with UPFC. The sequential method and the simultaneous or combined method. In sequential method the equations of UPFC are separated from the system power balance equations. Both the set of equations are solved separately and sequentially. In combined method all the equations are combined into one set of non-linear algebraic equations. A jacobian matrix is then formed which is non symmetric in nature. The combined method is used in this paper.

### 2. PRINCIPLE FUNCTION OF UPFC

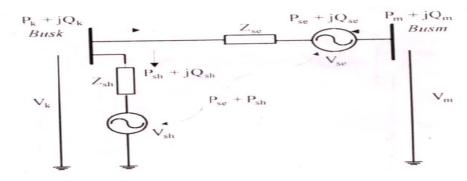

With the help of dc link the two voltage source converters of the UPFC are connected . It can be designed as two ideal voltage sources, one connected in series and the other in shunt between the two buses [9]. The output from series voltage source  $V_{se}$  and  $\theta_{se}$  are adjustable magnitude and angle between the limits  $V_{semax} \leq V_{se} \leq V_{semin}$  and  $\theta \leq \theta_{se} \leq 2\pi$  respectively and of the shunt voltage source is  $V_{sh}$  and  $\theta_{sh}$  adjustable between the limits  $V_{shmax} \leq V_{sh} \leq V_{shmin}$  and  $\theta \leq \theta_{sh} \leq 2\pi$ . Figure 1 shows the UPFC voltage source model.  $Z_{se}$  and  $Z_{sh}$  represents the impedances of the two coupling transformer one in series and other connected in shunt between the line and UPFC

Figure 1: Voltage source model of UPFC

T he output voltage of converter (magnitude and angle) is used to regulate the mode of power flow and voltage at the nodes as follows:

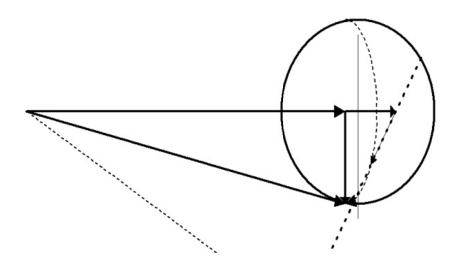

i) The magnitude of bus voltage can be adjusted by injecting a voltage  $V_{se}$  in phase or antiphase as shown in Figure. 2. ( $\theta_{se}$  is in phase/ antiphase with the nodal voltage angle  $\theta_k$ )

ii) Flow of power can be adjusted ( series reactive compensation) by injecting a voltage  $V_{se'}$  in quadrature (lead or lag ) to the line current (  $\theta_{se} = \gamma_m$   $\gamma_m$  is the angle between  $V_m$  and  $I_m$ )

iii) Flow of power can be regulated as phase shifter by voltage injection of magnitude ( $V_{se}$ ) in quadrature (lead or lag) to node voltage  $\theta_m$ .

Figure 2 : Combined control of voltage, impedance & angle

#### **3.MATHEMATICAL REPRESENTATION OF UPFC**

The voltage sources of the UPFC can be mathematically represented as:

$$\mathbf{V}_{se} = \mathbf{V}_{se} \left( \cos \theta_{se} + j \sin \theta_{se} \right)$$

(1)

$$V_{sh} = V_{sh} \left( \cos\theta_{sh} + j \sin\theta_{sh} \right)$$

(2)

UPFC is connected between two buses *k* and *m* in the power system. Applying the kirchoff's current and voltage laws for the network in Figure 1 gives:

$$I_{k} = (y_{se} + y_{sh})V_{k} + (-y_{se})V_{m} + (-y_{se})V_{se} + (-y_{sh})V_{sh}$$

$$I_{m} = (-y_{se})V_{k} + (y_{se})V_{m} + (y_{se})V_{se} + (0)V_{sh}$$

(3)

Where  $y_{se} = 1/z_{se}$  and  $y_{sh} = 1/z_{sh}$

The elements of admittance matrix can be written as

$$Y_{kk} = G_{kk} + jB_{kk} = y_{se} + y_{sh}$$

$$Y_{mm} = G_{mm} + jB_{mm} = y_{se}$$

$$Y_{km} = Y_{mk} + G_{km} + jB_{km} = -y_{se}$$

$$Y_{sh} = G_{sh} + jB_{sh} = -y_{sh}$$

(4)

Lossless UPFC converters are assumed in this voltage sources model. This implies that the two converters will not absorb or generate active power for its losses and the series converter active power demand at its output is supplied from the AC Power system by the shunt converters via the common D.C link. The DC link capacitor voltage  $V_{dc}$  remains unchanged. Hence the active power given to the shunt converter  $P_{sh}$  must be equal to the active power required by the series converter  $P_{se}$  at the DC link. Then the following equality constraint has to be represented

$$P_{se} + P_{sh} = 0 \tag{5}$$

From Figure. 1 and by Eq. (1), (2), (3) for the series and shunt sources the power equations of UPFC can be represented as

$$P_{se} = V_{se}^{2}G_{mm} + V_{se}V_{k}(G_{km}\cos(\theta_{se}-\theta_{k}) + B_{km}\sin(\theta_{se}-\theta_{k})) + V_{se}V_{m}(G_{mm}\cos(\theta_{se}-\theta_{k}) + B_{mm}\sin(\theta_{se}-\theta_{m}))$$

(6)

$P_{sh} = -V_{sh}^2 G_{sh} + V_{sh} V_k (G_{sh} \cos(\theta_{sh} - \theta_k) + B_{sh} \sin(\theta_{sh} - \theta_k))$ (7)

## 4.FAST DECOUPLED LOAD FLOW ALGORITHM

Fast decoupled load flow method requires considerably less time per iteration, and power solution is obtained very rapidly when compared to other load flow methods. Load flow algorithm is given below.

- 1. Read system data

- 2. Form bus admittance matrix Y<sub>bus</sub>

- 3. set convergence point  $\varepsilon$

- 4. set iteration count k=0

- 5. calculate active power P<sub>i</sub> and reactive power Q<sub>i</sub> for i=

2,...n with UPFC and shunt and series converter powers.

- 6. calculate change in active and reactive power for i=2,...n i.e., $\Delta P_i$  and  $\Delta Q_i$

- 7. calculate maximum absolute value of residue i.e.,  $|\Delta P_i|$ and  $|\Delta Q_i|$

- check if residue ≤ ε then go to step 15

else go to step 9

- 9. Form conventional jacobian matrix

- Modify jacobian matrix for incorporating UPFC Parameters

- 11. calculate B' and B'' matrices( these matrices are the imaginary part of bus admittance matrix

- 12. solve for  $\Delta |V|$ ,  $\Delta \delta$  using fast decoupled load flow equations mentioned below

$\Delta \delta = -[B']^{-1} \left( \Delta P / |V| \right)$

$\Delta \mid \mathbf{V}\text{= -}[\mathbf{B}^{\prime\prime}]\text{--}(\Delta \mathbf{Q} / \mid \mathbf{V} \mid$

- 13. Update bus voltages and UPFC output voltage

- 14. check if voltage magnitude of converter is out of limit then set voltages at limit values and advance iteration count and go to step 5 else advance iteration count and go to step 5

- 15. calculate line flows and bus powers and it ends the program.

## 5. IMPLEMENTATION OF UPFC IN FDLF ALGORITHM

The algorithm for solving a power flow problem embedded with UPFC is implemented by using the MATLAB programming

The Fast Decoupled load flow algorithm incorporating the UPFC is shown in previous section. The input system data includes the fundamental system data needed for conventional power flow calculation consisting of the number and types of buses, transmission line data, generation and load data, location of UPFC and the control variables of UPFC i.e the magnitude and angles of voltage output  $V_{se}$  and  $V_{sh}$  of two converters. The inclusion of the UPFC will increase one bus in the system. The UPFC power equations are combined with the network equations to give equation (8)

$$P_i + j Q_i = \sum_{j=1}^{n} V_I V_j Y_{ij \frown} (\theta_{ij} - \delta_i + \delta_j) + P_i' + j Q_i'$$

(8)

Where  $P_i' + jQ_i' =$  active and reactive power flow due to UPFC between the bus k and m.

$P_i + j Q_i$  = active and reactive power at the i<sup>th</sup> bus.

$V_i \leq \delta_i$ =voltage and angle of i<sup>th</sup> bus

$V_{ji} \Delta_j$ =voltage and angle of j<sup>th</sup> bus

$Y_{ij}$ = admittance of the transmission line between the bus i and j. Eq. (8) is linearised with respect to the variables of the network and the UPFC. The power flow constraint of the UPFC is included in the jacobian. The inclusion of these variables increases the dimension of the jacobian. The power equations are mismatched until the achievement of convergence. A scalar multiplier is used to control the variable updation to ensure that they converge in an optimised way to the solution point.

## 6. OPTIMISATION METHOD FOR CONVERGENCE

The Fast Decoupled method converge fails when working with automatic systems and highly loaded systems. Step size adjustment (optimal multiplier) technique is employed so that convergence property is improved.

In Fast Decoupled method the power balance contraints at any bus k of an n bus system, with the voltage source model of the UPFC, is represented as in equation(8).

These equations can be represented as s = f(x) = 0 where

x is vector of unknown, voltage and angle at each bus. The power flow attempts to solve

$$\mathbf{f}(\mathbf{x}) = \mathbf{0} \tag{9}$$

The taylor series expansion of (9) about the solution  $x^s$  at iteration t is  $f(x^s) = f(x^t + \Delta x^t) = f(x^t) + J(x^t)\Delta x^t + higher terms$  (10)

higher order terms are neglected here. Since  $f(x^s)=0$  by definition hence  $\Delta x^{t}=-[J(x^t)]^{-1}f(x^t)$ (11)

This result updates the current solution estimates. Thus

$$\mathbf{x}^{t+1} = \mathbf{x}^t + \Delta \mathbf{x}^t \tag{12}$$

$$\mathbf{x}^{t+1} = \mathbf{x}^t + \mathbf{\mu} \,\Delta \mathbf{x}^t \tag{13}$$

Instead of Eq (12), (13) is used where  $\mu$  is scalar multiplier used to ensure the convergence in an optimal manner. The mismatch at iteration t+1

can be written as

$$f(x^{t+1}) = f(x^t + \mu \Delta x^t) = f(x^t) + \mu J(x^t) \Delta x^t$$

(14)

Alternatively, the expression

$$C = 0.5 f^{T}(x)f(x)$$

(15)

defines a cost function that approaches zero as the system nears a solution. Differentiating (15) with respect to  $\mu$  yields the adjustment factor to use in evaluating  $x^{t+1}$ . This technique is used in obtaining convergence.

## 7. TEST CASE

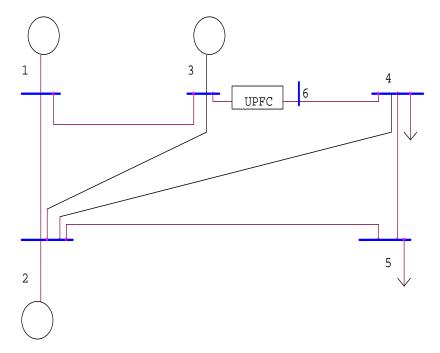

Standard 5 bus test network is considered with and without UPFC to investigate its behaviour as shown in Figure 3. In the analysis bus 1 is taken as slack bus or reference bus, bus 2 and 3 are generator buses and bus 4, 5 are load buses. In order to include UPFC in the network an additional bus (bus no 6) is introduced as shown. The shunt converter is set to control node 3 voltage magnitude at 1pu while series converter regulates the power flow between the two nodes. Assume Flat voltage profile for the two UPFC voltage sources.

| Test data is give | en below |

|-------------------|----------|

|-------------------|----------|

| Bus | Voltage     | Load   | Generator |       | Injected |

|-----|-------------|--------|-----------|-------|----------|

| no. | (   v   ,θ) | (MW,   | (MW,      | Qmin, | MVAR     |

|     |             | Mvar)  | Mvar)     | Qmax  |          |

| 1   | 1.06, 0     | 0, 0   | 0,0       | 10,50 | 0        |

| 2   | 1.045, 0    | 10, 20 | 40,30     | 10,50 | 0        |

| 3   | 1.03, 0     | 20,15  | 30,10     | 10,40 | 0        |

| 4   | 1.00, 0     | 50,30  | 0,0       | 0,0   | 0        |

| 5   | 1.00, 0     | 60,40  | 0,0       | 0,0   | 0        |

| 6   |             | 30, 2  |           |       |          |

Table 1Bus data

| Sending | Receiving | Line       | Line      | Line        |

|---------|-----------|------------|-----------|-------------|

| Bus     | Bus       | resistance | reactance | susceptance |

|         |           | p.u        | p.u       | p.u         |

| 1       | 2         | 0.02       | 0.06      | 0.06        |

| 1       | 3         | 0.08       | 0.24      | 0.05        |

| 2       | 3         | 0.06       | 0.18      | 0.040       |

| 2       | 4         | 0.06       | 0.18      | 0.040       |

| 2       | 5         | 0.04       | 0.12      | 0.030       |

| 3(6)    | 4         | 0.010      | 0.03      | 0.020       |

| 4       | 5         | 0.08       | 0.24      | 0.050       |

Table 2 Line data

# 8. SIMULATION RESULTS

The network was analysed without UPFC and with UPFC. For the network without UPFC the convergence was achieved in 6 iterations. With UPFC convergence was achieved in 8 iterations . Also, the UPFC parameters were found to be within limits. The simulation results shows the power flow for lines and bus active and reactive powers which are tabulated below. The voltages of the buses with and without UPFC are also tabulated.

| Line | Line Flows without Line Flows with UPFC |           |          | with UPFC |

|------|-----------------------------------------|-----------|----------|-----------|

|      | UPFC                                    |           |          |           |

| No.  | P (MW)                                  | Q(MVAR)   | P(MW)    | Q(MVAR)   |

| 1-2  | -0.86857                                | -0.72919  | 0.62169  | -0.033919 |

| 1-3  | -0.40284                                | -0.17524  | -0.2283  | -0.16788  |

| 2-3  | -0.24574                                | -0.003624 | -0.09029 | -0.2010   |

| 2-4  | -0.27353                                | -0.008406 | -0.20719 | -0.22803  |

| 2-5  | -0.53546                                | -0.048393 | -0.51328 | -0.3850   |

| 3-4  | -0.19357                                | -0.06566  | -0.40937 | -0.022    |

| 4-5  | -0.04699                                | -0.051809 | -0.09907 | -0.0149   |

Table 3 Line flows with and without upfc

| Bus | Bus Pc | ower without | Bus    | Power with |  |

|-----|--------|--------------|--------|------------|--|

| No. | UPFC   |              | UPFC   |            |  |

|     | P (MW) | Q(MVAR)      | P(MW)  | Q(MVAR)    |  |

| 1   | 1.3123 | 0.90927      | 0.8422 | 0.20288    |  |

| 2   | 0.41   | -0.62593     | 0.41   | 0.84573    |  |

| 3   | -0.46  | -0.19        | -0.12  | -0.299     |  |

| 4   | -0.41  | 0.05         | -0.51  | -0.31      |  |

| 5   | -0.61  | -0.1         | -0.61  | -0.41      |  |

| 6   | -      |              | -0.32  | 0.021      |  |

Table 4 Bus powers with and without upfc

It is observed from the Table 4 that the power of the 4<sup>th</sup> bus is increased due to the inclusion of UPFC powers .The power flow in the line between bus 3-4 has increased from -0.19357 to -0.40937. The negative sign indicates the direction of power flow from the shunt converter end to the series converter end. The bus voltages with and without UPFC is tabulated below. The UPFC is modelled to set the third bus voltage to 1 per unit.

Table 5 Bus voltage with and without upfc

| Bus | Voltage<br>UPFC | without | Voltage with UPFC |              |

|-----|-----------------|---------|-------------------|--------------|

| no  | V               | θrad    | V                 | θrad         |

| 1   | 1.06            | 0       | 1.06              |              |

| 2   | 1.047           | -2.4621 | 1.045             | 0<br>-1.8597 |

| 3   | 1.03            | -4.2711 | 1.00              | -1.9965      |

| 4   | 1.0187          | -4.6648 | 0.99151           | -3.0893      |

| 5   | 0.9899          | -5.3276 | 0.98121           | -4.4398      |

## 8. CONCLUSION

Voltage source model of UPFC is successfully used in this paper to determine the performance of UPFC in power flow control. Load flow analysis results for the standard

5 bus network has been presented with and without UPFC and compared. It was found that the UPFC regulates the voltage of the bus as well as the active and reactive power of the buses and the lines with in specified limits. The algorithm is capable of regulating the power flow and voltage singly as well as simultaneously. Hence UPFC with fast decoupled algorithm performed well in power system network and simulation results demonstrate that the proposed method is feasible for active power, reactive power, and voltage control in power system network.

## REFERENCES

- [1] N.G.Hingorani and L.Gyugyi, "Understanding FACTS," Concepts and Technology of Flexible AC Transmission Systems.IEEE press,2000

- [2] L.gyugi, "A unified power flow concept for flexible AC transmission systems," IEEE proc.c 139(4)1992.

- [3] J K.R.Padiyar and K.uma rao, "Modelling and control of unified power flow controller for transient stability," Electrical power and energy Systems, vol 21 (1999) 1-11.

- [4] H.f.wang, "Interactions and multi variable design of unified power flow controller," Electrical power and energy systems 24(2002).

- [5] A.W.Green, J.T.Boys, "Threephase voltage sourced reversible rectifiers," IEEE proc.135(1988)362-370.

- [6] K. Manoz kumar reddy, "Simulation of unified power flow controller," proceedings of National conference on recent trends in power systems and power electronics, (Feb 2012)148-151.

- [7] M.kowsalya, K.K.Ray, and D.P.Kothari, "Loss optimization for voltage stability enhancement incorporating UPFC using particle swarm optimization," Journal of electrical engineering & technology Vol 4, No.4, pp.492-498.2009

- [8] K. Manoz kumar reddy, "Increasing dynamic stability of the network using UPFC," Iosr journal of engineering, vol.2(4), April 2012, pp 744-749.

- [9] Niklesh kumar Sharma et al, " A novel placement strategy for facts controllers" IEEE transactions on power delivery, Vol.18, No.3, july 2005, pp 982-987.