# AN EFFICIENT IMPLEMENTATION OF DWT FOR IMAGE COMPRESSION ON RECONFIGURABLE PLATFORM

Altaf O. Mulani<sup>1</sup> and Dr. P. B. Mane<sup>2</sup>

*Abstract:* Image compression is a significant technique in storage and transmission of digital images as it requires huge data. This paper presents an efficient implementation of Discrete Wavelet Transform (DWT) for image compression on reconfigurable platform. This implementation can be applied for lossy as well as lossless compression. The system is implemented using VHDL and simulated using MATLAB. The experimental result shows that this implementation occupies only 144 slice registers at an operating frequency of 43.630 MHz.

Key Words: DWT, FPGA, VHDL, image compression, JPEG

#### **I. INTRODUCTION**

Now-a-days, demand and development of multimedia information is growing rapidly which further contributes to insufficient network bandwidth and memory storage. Due to this, data compression becomes more significant for reducing the data redundancy to save memory storage and transmission bandwidth. DWT based image compression such as JPEG 2000 offers major features such as high compression efficiency, lossless color transformation, region-of-Interest Coding, lossless and lossy compression, random code stream access and processing error resilience. DWT is an application of sub-band coding. In sub-band coding, input spectrum is decomposed into set of band limited components called sub-bands. These sub-bands can be assembled to reconstruct the original spectrum without an error.

DWT has become one of the most commonly used techniques for signal analysis and image processing applications. DWT performs multiresolution signal analysis that holds both time and frequency information. Due to its time and frequency domain characteristics, DWT has been widely used for image compression such as in JPEG 2000. Generally, (5/3) and (9/7) wavelet filters are used as default filters for lossless and lossy compression respectively. Since convolution method is based on filter bank structures in implementation of DWT, large number of arithmetic computations and large storage area is required. It also requires features that are not desirable for either high speed or low power hardware applications. Many VLSI based 1-D and 2-D DWT architectures have been developed and implemented to reduce number of slices, internal memory requirements, hardware complexity and increase the design performance.

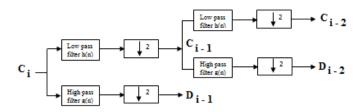

DWT has been widely used in applications of digital signal processing due to its efficient computation and sufficient characteristics for non-stationary signal analysis. Generally, the structure used for wavelet analysis is as shown in the figure 1.

<sup>&</sup>lt;sup>1</sup>Research Scholar, Department of Electronics and Telecommunication Engineering, Sinhgad College of Engineering, Pune, Maharashtra, India, Email- aksaltaaf@gmail.com

<sup>&</sup>lt;sup>2</sup> Department of Electronics and Telecommunication Engineering, AISSMS Institute of Information Technology, Pune, State, Maharashtra, India

where Cx = Approximation coefficients

Dx = Detail coefficients

#### Figure 1. One-dimensional DWT decomposition

DWT decomposes a signal into different sub-bands in order to get the lower frequency subbands that have finer frequency resolution and higher frequency sub-bands for coarser time resolution. Decomposition of an image can be single level, two level or three level as shown in figure 2.

| LL              | HL                             | LL | HL. | HL                          | LL HL<br>LH HH | HL | HL                            |  |  |

|-----------------|--------------------------------|----|-----|-----------------------------|----------------|----|-------------------------------|--|--|

|                 | III.                           | LH | НН  |                             | LH             | HH |                               |  |  |

| LH              | нн                             | LH |     | нн                          | L              | н  | нн                            |  |  |

| (a) Single Leve | (a) Single Level Decomposition |    |     | (b) Two Level Decomposition |                |    | (c) Three Level Decomposition |  |  |

Figure 2. DWT Decomposition

DWT evaluates the signal at dissimilar frequency bands with different resolutions by disintegrating the signal into an approximation and detail information. Decomposition of a signal into diverse frequency bands obtained by successive high pass filtering g[n] and low pass filtering h[n] of the time domain signal. The combination of high pass g[n] and low pass filter h[n] encompass a pair of analyzing filters. Output of each filter comprises half the frequency content, but an equal amount of samples as the input signal. Two outputs together comprise the same frequency content as that of input signal; however, the amount of data is doubled. Hence, in the analysis bank, down sampling by two is applied to the outputs of the filters.

DWT is widely used for image compression as it supports features like easy manipulation of compressed image, progressive image transmission, region of interest coding, etc.

#### 1.1. One-Dimensional DWT:

Initially, the signal is applied to low-pass (LP) and high-pass (HP) filters respectively. Then, the output of these filters (i.e. filtered coefficients) are down sampled to neglect the alternate coefficients. When the output of low-pass filter is down sampled, it contains low frequency components of the signal which are known as approximate portion of the original signal whereas when the output of high-pass filter is down sampled, it contains high frequency components which are known as detailed portion of the original signal. The filter pair low-pass filter h(n) and high-pass filter g(n) used for decomposition of the signal is known as analysis filter-bank whereas filter pair used for reconstruction of the signal is known as synthesis filter bank.

The output of low-pass filter h(n) represents the approximate coefficients and is represented as:

$$y_h(n) = \sum_k x(k)h(2n-k)$$

The output of high-pass filter g(n) represents the detailed coefficients and is represented as:

$$y_g(n) = \sum_k x(k)g(2n-k)$$

#### **II. LITERATURE SURVEY:**

This section provides the overview about some of FPGA and MATLAB oriented implementations of DWT algorithm:

Altaf O. Mulani el at [1] presented a combined watermarking and cryptography approach for image authentication. This implementation occupies 2117 slices at maximum operating frequency of 228.064 MHz. This scheme provides improved security without compromising its speed and area.

Venkata Anjaneyulu el at [2] focused their interest on memory efficient FPGA for SPIHT (Set Partitioning in Hierarchical Trees) image compression technique.

P.R.Kulkarni el at [3] suggested robust invisible watermarking for image authentication which is better to retain the original image.

M. Nagabushanam el at [4] proposed a modified lifting scheme based 1D and 2D DWT FPGA architectures for computing the approximation and detailed coefficients of DWT. The system is implemented on Virtex-5 and it requires 1152 slices at 180 MHz.

P.R.Kulkarni el at [6] proposed DWT based robust invisible digital image watermarking which does not affect the quality of original image. This method first combines information of low frequency DWT coefficients and watermark image and then the combination of this is used to extract the watermark.

M. Puttaraju el at [7] proposed FPGA oriented (5/3) integer DWT for image compression. This architecture is based on lifting scheme and can be applied to 2D spatial images from payload instruments.

Durga Sowjanya el at [8] proposed an area efficient and high speed VLSI architecture that utilizes 158 slices at 120 MHz. This implementation requires least computing time and also less area. It is applicable for fixed point 1-D DWT.

M. Nagabushanam el at [9] suggested DWT architecture based on modified BZFAD multiplier that occupies 1152 slices at 256 MHz. According to the author, this implementation is 65 % faster and occupies 44 % less area. It also achieves 35 % power saving.

Abdullah Al Muhit el at [13] proposed a DWT algorithm for image compression which supports JPEG 2000 standards.

#### **III. PROPOSED ALGORITHM**

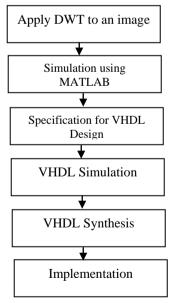

The flow graph of proposed algorithm is as shown in figure 3.

Fig. 3. Proposed Algorithm

Initially the code of the algorithm was written using MATLAB because it provides powerful numerical computation and advanced visualization with easy to write syntax. DWT algorithm has been tested on the "lena" image file with satisfactory result. After achieving proper result, we move to HDL coding using Xilinx\_ISE\_Design Suite\_13.1. Here, initially specification of the algorithm at the behavioral level is carried out using the HDL. After compilation, algorithm was simulated using Questasim to get the satisfactory results for real time implementation. Next, the HDL codes are synthesized using the Xilinx XST synthesis tool which will produce gate-level architecture for FPGA implementation. Finally, the design codes of DWT will be downloaded into FPGA board for verifying its functionality. However, in this paper we only present the simulation results for the DWT.

## **IV. EXPERIMENT AND RESULT**

## 4.1. Tools Used in the Design

## Software tools:

Xilinx ISE\_Design Suite\_13.1 and MATLAB 2014 are used for this implementation. Xilinx ISE\_Design Suite\_13.1 is used for simulation as well as synthesis purpose. Additionally, Questasim is used for simulation and MATLAB 2014 is used to read the output.

## Hardware tools:

Xilinx Virtex series FPGA XCV400 is used which has following characteristics as shown in table 1:

| Characteristics | Value |

|-----------------|-------|

| LUTs            | 9600  |

| Slices          | 4800  |

| IOBs            | 170   |

Table 1: Characteristics of XCV400

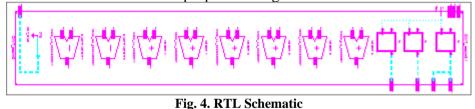

## 4.2. RTL Schematic:

Figure 4. shows the RTL schematic of our proposed design.

#### 4.3. Comparative Analysis:

It is very important to compare the performance of proposed design with existing implementations to evaluate its performance or efficiency. The comparison can be done based on area utilized and its operating frequency. There are various FPGA based implementations some of which requires less area and some achieves optimum speed.

Table 3 shows the comparison of the result obtained in this proposed design with previously obtained results.

| Parameters      |    | Our Work | Reference | Reference | Reference |

|-----------------|----|----------|-----------|-----------|-----------|

|                 |    |          | [2]       | [6]       | [5]       |

| Slice registers |    | 144      | 1152      | 1152      | 158       |

| Frequency       | of | 43.630   | 180 MHz   | 256 MHz   | 120 MHz   |

| Operation       |    | MHz      |           |           |           |

| FPGA used       |    | Virtex   | Virtex-V  | Virtex-V  | Virtex-II |

|                 |    | Virtex   | Virtex-V  |           | Virtex-I  |

#### 4.4. Simulation Results: Figure 5. shows simulation result for lena image.

a. Input image

b. Single level decomposed image

c. Reconstructed Image Fig. 5. Simulation Result

#### **V.CONCLUSION**

In this paper, area efficient and high speed DWT algorithm for image compression is suggested. This implementation requires only 144 slices at an operating frequency of 43.630 MHz. And from the comparison with previous work done, it is clear that proposed algorithm is better from area as well speed point of view.

#### REFERENCES

- [1]

- Altaf O. Mulani and P.B.Mane, "Area efficient high speed FPGA based Invisible Watermarking for Image authentication", Indian Journal of Science and Technology, Vol. 9, Issue 39, Oct. 2016 Venkata Anjaneyulu and P. Rama Krishna, "FPGA Implementation of DWT SPIHT Algorithm For Image Compression", International Journal Of Technology Enhancements And Emerging Engineering Research (IJTEEE), 2014. [2]

- Engineering Research (DTEEE), 2014.

P. R. Kulakarni, A. O. Mulani and Dr.P. B.Mane, "Robust Invisible watermarking for image authentication", IEEE International Conference on Emerging Trends in Electrical, Communications and Information Technologies (ICECIT-2015), Dec. 2015.

M. Nagabushanam, S. Ramachandran and P.Kumar, "FPGA Implementation of 1D and 2D DWT Architecture using Modified Lifting Scheme", WSEAS transactions on Signal Processing, 2013.

Naseer M. Basheer, Mustafa Mushtak Mohammed, "Design and FPGA Implementation of a Lifting Scheme 2D DWT Architecture", International Journal of Recent Technology and Engineering (IJRTE), 2013.

- P. R. Kulakarni and A. O. Mulani, "Robust Invisible Digital Image Watermarking using Discrete Wavelet Transform", International Journal of Engineering Research & Technology (IJERT), Vol. 4 Issue 01, pp.139-141, Jan. 2015. [6]

- M. Puttaraju and Dr.A. R. Aswatha, "FPGA Implementation of 5/3 Integer DWT for Image Compression", International Journal of Advanced Computer Science and Applications (IJACSA), [7]  $2012^{r}$

- Durga Sowjanya, K N H Srinivas and P Venkata Ganapathi, "FPGA Implementation Of Efficient VLSI Architecture For Fixed Point 1-D DWT Using Lifting Scheme", International Journal of VLSI design & Communication Systems (VLSICS), 2012. [8]

- Nagabushanam M. and Ramachandran S., 'Fast implementation of lifting based 1D/2D/3D DWT-IDWT architecture for image compression', International journal of computer Applications, 2012. [9]

- [10] M. Jeyaprakash, "FPGA Implementation of Discrete Wavelet Transform (DWT) for JPEG 2000", International Journal of Recent Trends in Engineering, 2009.

- [11] J. Jyotheswar and Sudipta Mahapatra, "Efficient FPGA implementation of DWT and modified SPIHT for lossless image compression", Journal of Systems Architecture, 2007.

- [12] Abdullah Al Muhit, Md. Shabiul Islam and Masuri Othman, "Design and Analysis of Discrete Wavelet Transform", International Conference on Parallel and Distributed Processing Techniques and Applications, 2005.

- [13] Abdullah AlMuhit, Md. Shabiul Islam and Masuri Othman, "VLSI Implementation of Discrete Wavelet Transform (DWT) for Image Compression", 2nd International Conference on Autonomous Robots and Agents, 2004

- [14] J. R. Ohm, M. van der Schaar, and J. W. Woods, "Interframe wavelet coding: Motion picture representation for universal scalability," *J. Signal Processing Image Communication*, 2004.

[15] Andra K, Chakrabarti C. "A VLSI architecture for lifting-based forward and inverse wavelet transform", IEEE Transaction on Signal Processing, 2002.

[16] Skodras, C. Christopoulos and T. Ebrahimi, "The JPEG 2000 still image compression standard," *IEEE Signal Processing Magazine*, 2001.

[17] Daubechies I, Sweldens W. "Factoring wavelet transforms into lifting schemes," J. Fourier Analysis Application, 1998.