# Design of Low Area Static CMOS Parallel Self-Timed Adder with Low Power Consumption using Conditional Approach

K.V. Ganesh\* and V. Malleswara Rao\*\*

*Abstract :* Adder is an important circuit used in arithmetic and logic unit and many other applications. There are different types of algorithms used in adders to achieve better performance, low Area and low Power. The main objective of this paper is to provide new low power, area efficient solution for very large scale integration (VLSI) Circuit designers. We have many logic styles such as Swing Restored complementary Pass-transistor Logic (SR-CPL) and Dual Pass-Transistor (DPL), dynamic logic and static logic. Adder has been designed by using Static CMOS logic and it has the disadvantage of more Transistor count .we will also ensure that speed will not be worse by making sure that not more than four number of transistors are in series either in pull-up or pull-down network of CMOS. Cells which were being used has limited fan-in as well as fan-out, though asynchronous logic is employed. The proposed Adder has been designed and simulated by using TANNER EDA Tool.

Keywords: Static cmos, conditional approach, xor, mux.

## 1. INTRODUCTION

Adder used Transmission gates which does not have Power rails, Static CMOS which has only Disadvantage of more number of Transistors and Pseudo NMOS logic which has charge sharing problems[1]. Wave pipelining is a method to increase the Performance of the system and Clock period of such a system is difference of Maximum and Minimum delay[2]. Carry signals are organized in a Tree manner but not in a Chain fashion which degrades the Speed[3]. Asynchronous systems has more performance and low Power but they are difficult to design and computation will be done only when necessary[4].CMOS has reliable operation as well as high noise margins even though the Voltage is scaled which means logic levels will be degraded and it also supports minimum number of Transistor sizes[5]. Multi threshold CMOS technologies has circuits with uneven threshold voltages like more is the threshold voltage more is the delay so reduction in threshold voltages will be done for Transistors which are involved in the Critical path so that Critical path performance can be enhanced[6]. Adder has been designed in many logic styles to analyze the results but still 28T Full Adder is the Designer choice in most cases as it is Designed in Static CMOS, though it supports limited Fan-out it can be made better by introducing Buffers[7]. Adder has been designed in pass transistor logic which has problem of Logic level degradation and it also has non-uniform structure[8]. There is a recommendation that not more than four number of Transistors should be there in series either in pull-up or pull-down region[9]. Asynchronous Adders are based on full dual rail encoding of all the signals and these are difficult to design when in compared with Synchronous circuts[10].

<sup>\*</sup> Ph.D Scholar, Dept of ECE, GITAM University, Visakhapatnam, Andhra Pradesh, India, kona.venkat13@gmail.com

<sup>\*\*</sup> Professor, Dept of ECE ,GITAM University, Visakhapatnam, Andhra Pradesh, India, mraoveera@yahoo.com

## 2. CONDITIONAL APPROACH

|            |      | 50    | -    | 20   | X D | 6  |            | 1   | 1.a.I. | 4 66  | -       | - | * | <b>X</b>   |                |       |       |     |  | 1 | ſ | 34, | 201 |

|------------|------|-------|------|------|-----|----|------------|-----|--------|-------|---------|---|---|------------|----------------|-------|-------|-----|--|---|---|-----|-----|

|            | al D | - 100 |      | 12   |     |    | a <u>~</u> |     |        | 4 0.0 |         |   | - | 1000   100 |                |       |       |     |  | Ľ |   |     | ,   |

|            |      |       | E    |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

| 00800071/1 | ×    |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

| 00         |      |       |      |      |     |    |            |     |        |       |         |   |   |            | G              |       |       |     |  |   |   |     |     |

| 000        |      |       |      |      |     |    |            |     |        |       |         |   |   |            | Y              | W = ( | ).54ı | J _ |  |   |   |     |     |

|            |      |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

| 2          | •    |       |      |      |     |    | -          |     |        |       |         |   |   |            |                | _=0   | .18u  |     |  |   |   |     |     |

| 11         | ÷    |       |      |      |     |    | Inp        | but | 1      |       | $\succ$ |   |   |            | $\blacksquare$ | φ     |       |     |  |   |   |     |     |

| _          | -    |       |      |      |     |    |            |     |        | _/    |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | ÷    |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | -    |       |      |      |     |    |            |     |        |       |         |   |   |            | $\bigcirc$     |       |       |     |  |   |   |     |     |

|            |      |       |      |      |     |    |            |     |        |       |         |   |   |            | 0              |       |       |     |  |   |   |     |     |

|            |      |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | ·*-  |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | .+.  |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | 2    |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            | 8    |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            |      |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

|            |      |       |      |      |     |    |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

| ECT        |      | MOVE  | EDIT | SELE | CT  | -1 |            |     |        |       |         |   |   |            |                |       |       |     |  |   |   |     |     |

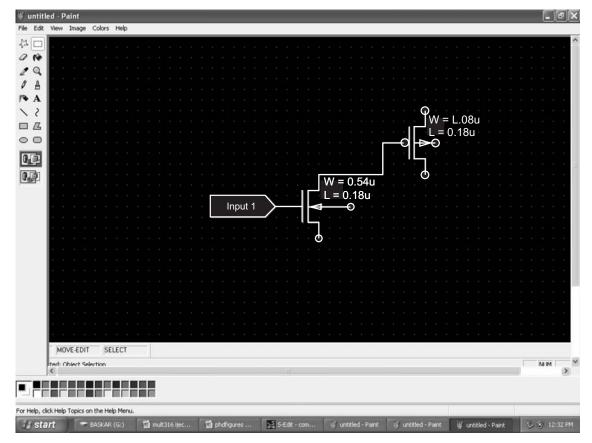

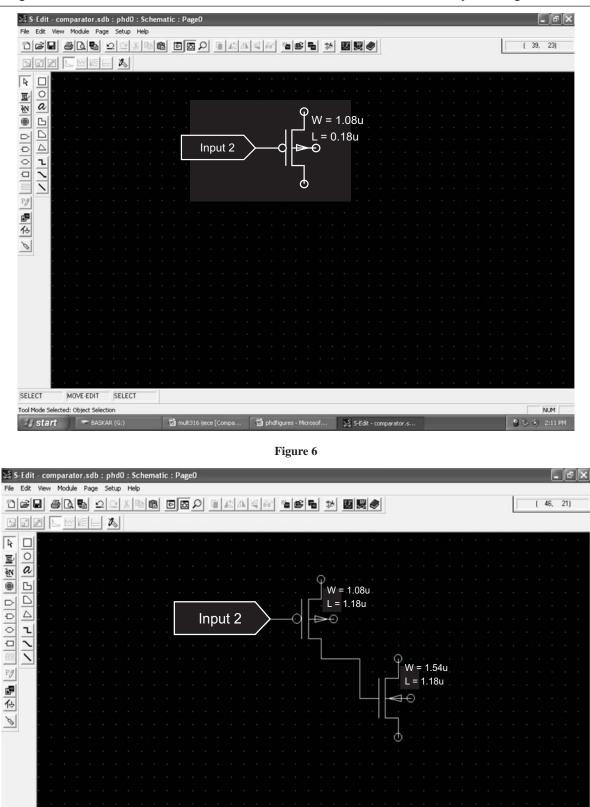

### Figure 1

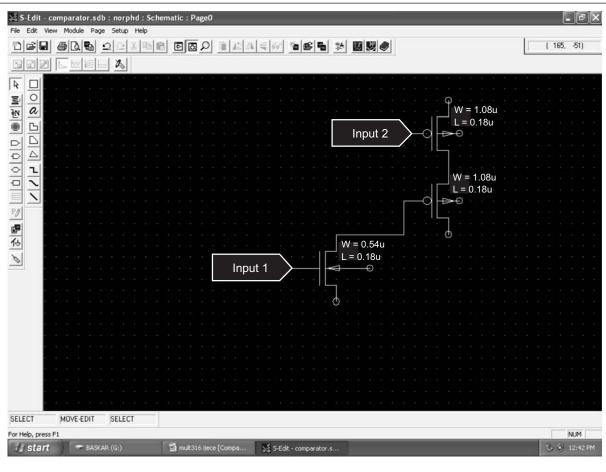

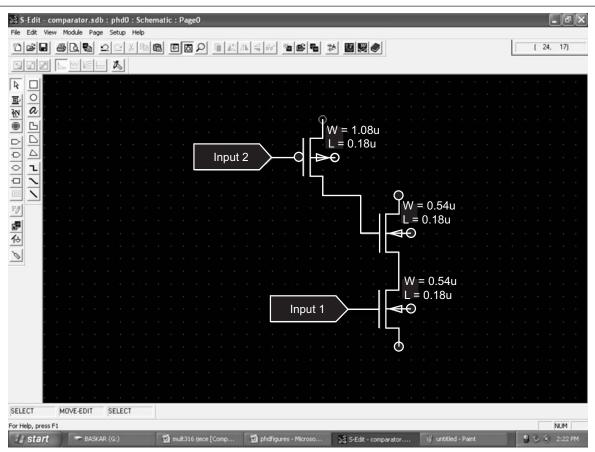

#### Figure 3

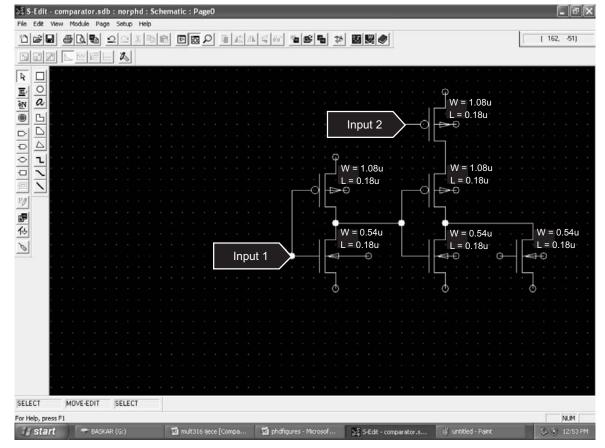

Figure 4

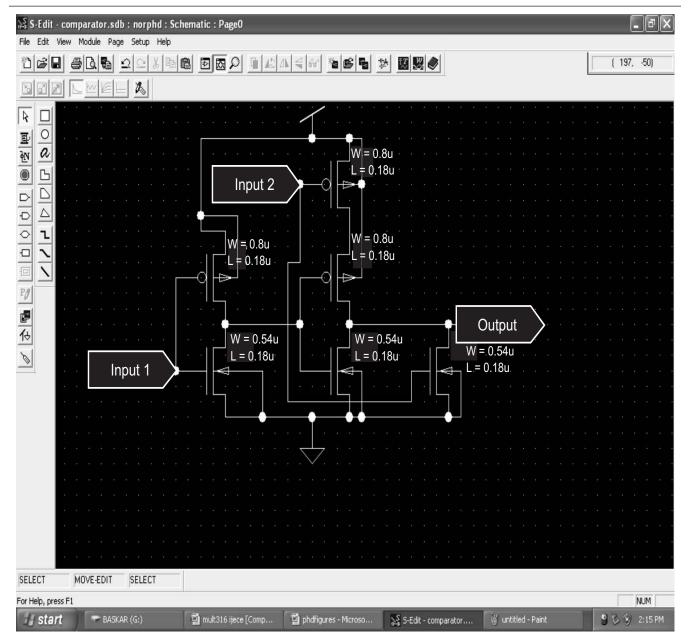

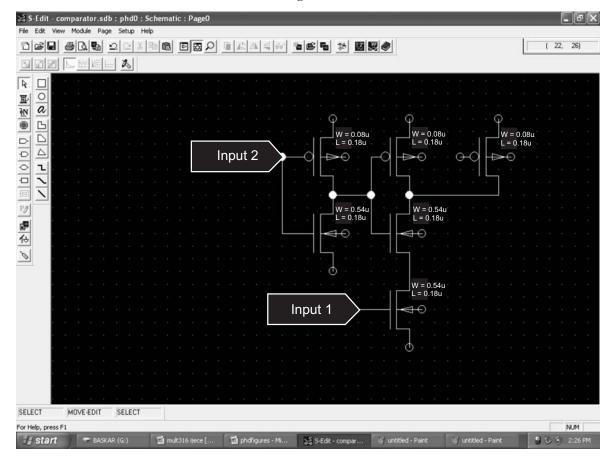

### Figure 5

In this paper we introduce a new kind of method called conditional approach as follows, When there are 2 inputs and in which if one input is High and other input is Low, it is clear that 2 Demarcation lines are needed because High corresponds to NMOS and Low corresponds to PMOS but whether NMOS to be placed in the First Demarcation line and PMOS to be placed in the Second Demarcation line or Vice versa depends on Output Low(High) requirement and it will be in the form of NMOS – PMOS if Output required is High because through PMOS we will get '1', in the form of PMOS – NMOS if Output required is Low because through NMOS we will get '0', and from First Demarcation line we can get either '0' or '1' so 1 extra PMOS and NMOS for this purpose and anyhow if First Demarcation line has NMOS there will be PMOS and same is the case with Second Demarcation line.

Let us see the assumed condition for Output(high) step by step procedure Applying the conditions for Output(Low) as followed by steps

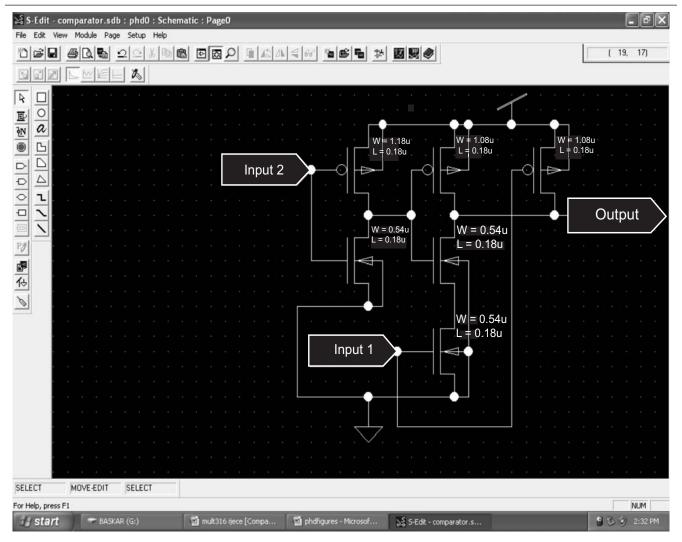

Figure 7

phdfigures - Microsof..

S-Edit - comparator.s...

📓 mult316 ijece [Compa...

NUM

9 3 8 2:18 PM

SELECT

For Help, press F1

🛃 start

MOVE-EDIT SELECT

🖙 BASKAR (G:)

Figure 8

### Figure 10

The approach which we have presented here can be extendable to N-bit it's like with N inputs we will be having combinations's high's and Low's and if requirement is like I1, I3, I4, I6, I7 are High's and I2,I5,I8(IN) are Low's then all the High corresponding inputs are NMOS Transistors in series but whether in the First Demarcation line or in the Second Demarcation line depends on Output High(Low) requirement, all the Low corresponding inputs are PMOS Transistors in series but whether in the First Demarcation line or in the Second Demarcation series but whether in the First Demarcation line or in the Second Demarcation line depends on Output High(Low) requirement, all the Low corresponding inputs are PMOS Transistors in series but whether in the First Demarcation line or in the Second Demarcation line depends on Output Low(High) requirement,

### 3. ADDER

We have designed Adder by taking the general block diagram of PASTA[1] in which it has blocks like MUX, Half-Adder and Completion Detection Unit. MUX has been designed by using Static CMOS, Half-Adder sum part designed by using Transmission gate based CMOS and carry part by Static CMOS, and Completion Detection Unit by using Dynamic logic

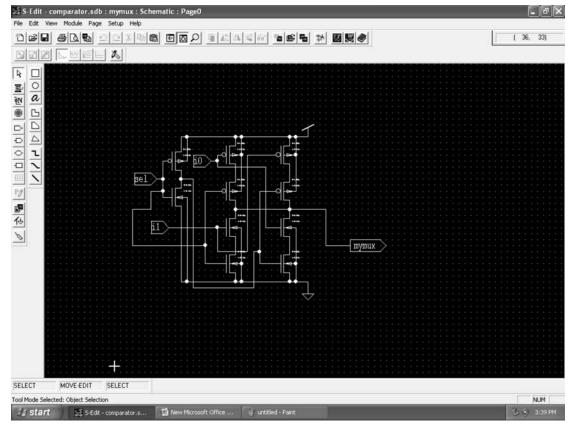

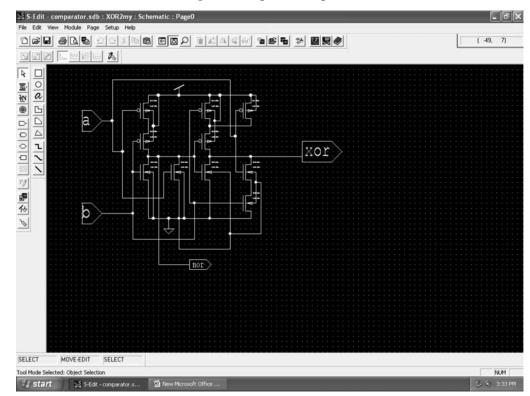

We have developed our own blocks named mymux, XOR and Completion Detection Unit, all these were designed by using Static CMOS. MUX in PASTA[1] can be replaced with mymux, Half-Adder in PASTA[1] can be replaced with myXOR and Completion Detection Unit is the same but designed with Static CMOS.

Mymux block is just the complemented output of MUX, MyXOR block has two outputs, in general XOR gate has only one output but the XOR which we have designed has two outputs and it is like utilizing efficiently Demarcation lines and our block has two Demarcation lines one has function of NOR

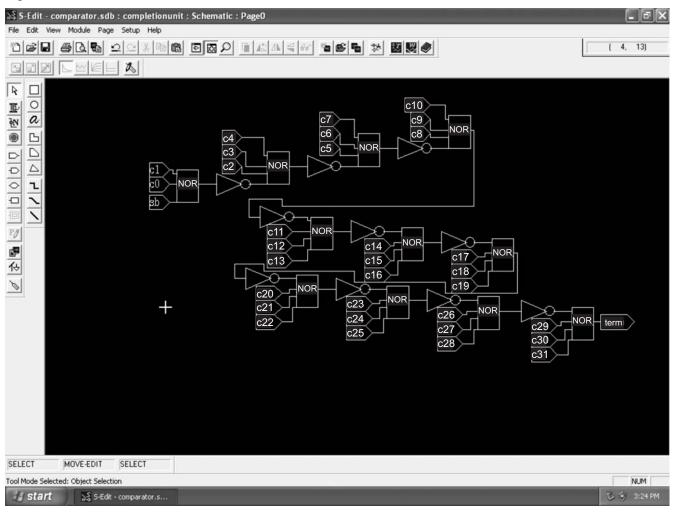

other has function of XOR. Since mymux block is designed in a complemented manner, NOR gate can implement required function. Completion Detection Unit has very high fan-in it is nearly N+1 where N is total number of bits. To avoid speed degradation buffers can be introduced and requirement of how many buffers is directly proportional to N. Even though this approach needs to sacrifice Area it is mandatory.

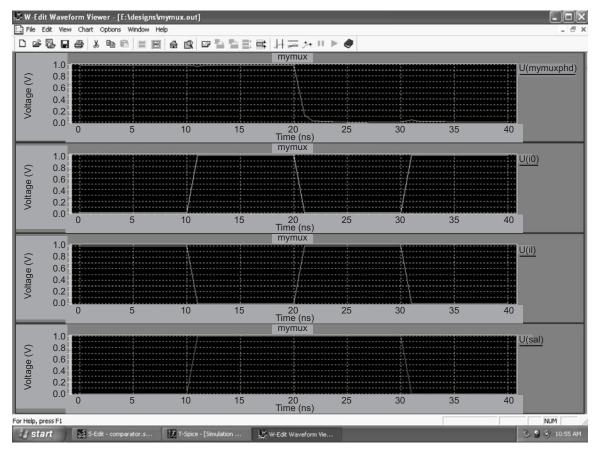

Figure 11: Proposed Multiplexer

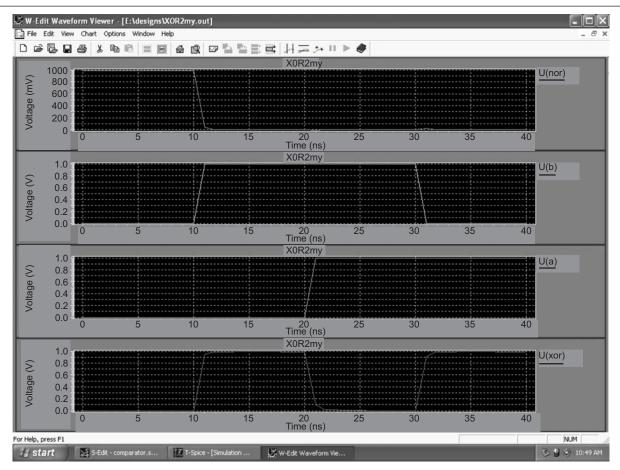

Figure 12: Two input – Two output XOR block

Proposed mux has 10 number of Transistors and when sel = '0' then complement of I0 will be selected and when sel = '1' then complement of I1 will be selected.

XOR block has 10 number of transistors and it has two outputs first Demarcation line has nor function and second Demarcation line has xor function, it has two sub-circuits in it one is nor circuit other is AOI 21

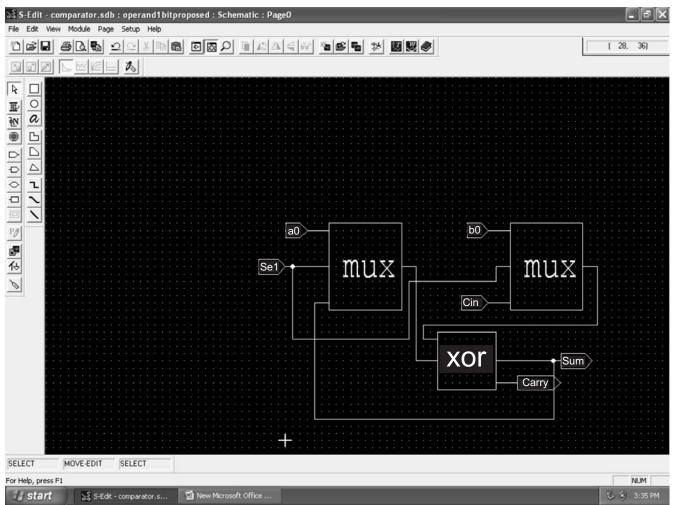

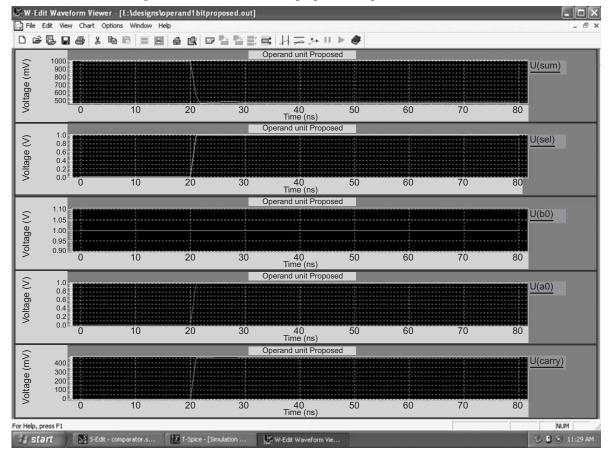

Figure 13: Proposed 1-bit operand block

1-bit operand block has two 2 to 1 MUX and one XOR, and XOR second output is carry and sum output is fed back to the MUX

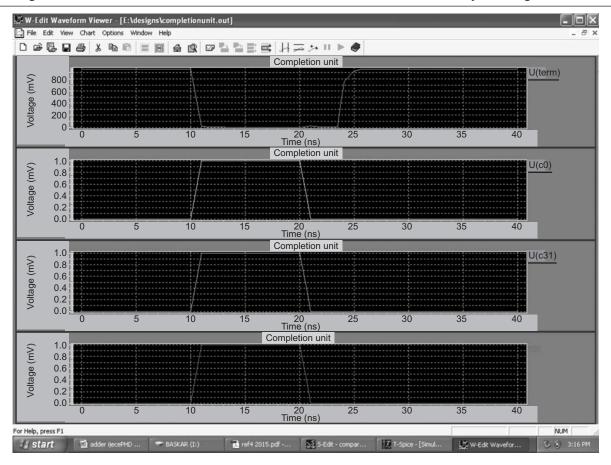

Completion Detection Unit has one 3-input nor gate which requires 6 Transistors, ten not gates which requires 20 Transistors and ten 4-input nor gate which requires 80 Transistors leading to a total of 106 Transistors. Here fan-in is very much limited even though transistor count is increased for sure speed will be enhanced.

## 4. STATIC CMOS

The main advantage of Static CMOS is Robustness, low power consumption as well as Full output voltage swing if P-MOSFET is ON condition then N-MOSFET is OFF. More number of transistors required for Static CMOS, we require T-number of transistors in the PULL-DOWN network. WHILE, in Static CMOS network T-number of transistors in pull up network ARE PRESENT. The full voltage levels can make sure in the upcoming section's N-MOSFET'S and P-MOSFET'S fully on or off AS STATIC CMOS has advantage of full output voltage swing .if the output is Logic '1' and Logic '0' or vice versa the circuit can be designed. the differentiation between output voltage high logic level and output voltage low logic level

is easy and this will be even more beneficial when the technology is scaled down, the Logic '1' range and Logic '0' range will come down when the supply voltage is less. Even while it is recommended that not more than 4 number of transistors should be in series in PULL-UP or not more than 6 Transistors should be in series in PULL-DOWN region as delay is going to be worse, variation is because NMOS is faster than PMOS. Our Design has only 4 number of maximum Transistors in series of pull-up and 2 in number of pull-down.

Figure 14: Proposed Completion Detection Unit

## 5. PERFORMANCE ANALYSIS

Table 1Comparison Report for Area of Mux 2 To 1

| Total                       | Design in Reference1 | Proposed Design (Static cmos) |

|-----------------------------|----------------------|-------------------------------|

| Area(number of transistors) | 12                   | 10                            |

Design of Adder which can be extendable upto N-bit are done by using STATIC CMOS logic style. AREA comparison of Mux shown in table 1 in which 2 transistors were reduced . AREA comparison of Half-Adder in which 6 transistors were reduced are shown in table 2. AREA comparison of 1-bit operand in which 10 transistors were reduced is shown in table 3. Table4 shows AREA comparison of N-bit operand in which N\*10 transistors were reduced are shown in table 4. AREA comparison of 32-bit Adder in which 248 transistors were reduced are shown In table 5. Table6 shows AREA comparison of 32-bit completion detection unit in which 72 transistors were increased due to Static CMOS technology which by default takes less number of transistors and we have also further added many buffers to increase the speed.

# Table 2 Comparison Rreport For Half Adder

| Total                       | Design in Reference1 | Proposed Design (Static cmos) |

|-----------------------------|----------------------|-------------------------------|

| Area(number of transistors) | 16                   | 10                            |

#### Table 3

### **Comparison Rreport For 1-Bit Operand**

| Total                       | Design in Reference1 | Proposed Design (Static cmos) |

|-----------------------------|----------------------|-------------------------------|

| Area(number of transistors) | 40                   | 30                            |

### Table 4

### Comparison of Area in Two Designs For N-Bit Operand

| Total                       | Design in Reference1 | Proposed Design (Static cmos) |

|-----------------------------|----------------------|-------------------------------|

| Area(number of transistors) | N*40                 | N*30                          |

Table 5

### Comparison Report for 32-Bit Adder

| Total                       | Design in Reference1    | Proposed Design (Static cmos) |

|-----------------------------|-------------------------|-------------------------------|

| Area(number of transistors) | (32*40) + (32+2) = 1314 | (32*30) + 106 = 1066          |

## Table 6 Comparison of Area in Two Designs for 32-Bit Completion Detection Unit

| Total                       | Design in Reference1 | Proposed Design (Static cmos) |

|-----------------------------|----------------------|-------------------------------|

| Area(number of transistors) | 34                   | 106                           |

## Table 7 Comparison of Power in Two Designs for Mux

| Total                     | Design in Reference1         | Proposed Design (Static cmos) |

|---------------------------|------------------------------|-------------------------------|

| Average Power Consumption | 8.746993 <i>e</i> -010 watts | 6.511302 <i>e</i> -010 watts  |

| Table 8    |                                             |  |  |  |  |  |  |  |  |

|------------|---------------------------------------------|--|--|--|--|--|--|--|--|

| Comparison | of Power in Two Designs for Half-Adder(XOR) |  |  |  |  |  |  |  |  |

| Total                     | Design in Reference1         | Proposed Design (Static cmos) |

|---------------------------|------------------------------|-------------------------------|

| Average Power Consumption | 8.847008 <i>e</i> -010 watts | 7.058207 <i>e</i> -010 watts  |

Here Carry output has a function of NOR because in the earlier stage itself Multiplexer output is designed in the Complemented manner,

When selection line is equal to '0' or '1' then Complemented version of the corresponding input will be the output.

182

Figure 15: Simulation Result of Two input - Two Output XOR block

Figure 16: Simulation Result of proposed Mux

Figure 17: Simulation Result of proposed Completion detection unit

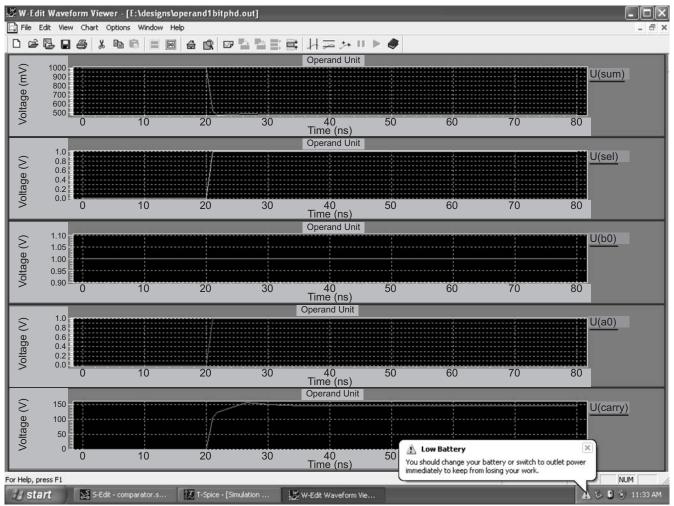

Figure 18: Simulation Result of proposed 1-bit operand unit

We were able to Design 32-bit unit by introducing many Buffers in the Circuit so Speed by Default will not be degraded and Area has been sacrificed to enhance the Speed and it does not have any problems of Dynamic circuits as in[1] where the Completion unit is being designed in Dynamic logic..

When in operand reading mode operands will be read then next feedback(Carry) path will be active and in which Carry output has 550 milli volts.

Figure 19: Simulation Result of 1-bit operand unit

Above result indicates that in feedback(Carry) path Carry output has only 150 milli volts.Power comparison reveals that cells which were being replaced has less power consumption. Since all the cells in our design based on Static CMOS, Layout optimization is also possible. One of the cells which are used in [1] are based on Dynamic logic which has charge sharing problems as well as more noise, another cell used Transmission Gates in there will be no power rails.

## 6. CONCLUSION

As area is proportional to Cost it has been a major constraint. Today Power and speed also started gaining more importance.our idea with the help of full custom design allows us to make our own circuit by taking the leaf level cells as gates or Transistors. Since, our Design is implemented in Transistors we have been able to optimize area and power constraints. Though we want Speed to be more , which is possible because of optimizing the logic, we haven't sacrificed on any Design constraint. we have designed our Adder by using STATIC CMOS logic that generally requires more number of transistors. while we are able to design the same by using less number of transistors . by following our approach we can achieve huge reduction in Transistor count, inspite of following the Architecture of PASTA, we have Redesigned the blocks.

### 7. **REFERENCES**

- 1. Mohammed Ziaur Rahman, Lindsay Kleeman, and Mohammad Ashfak Habib, "Recursive Approach to the Design of a Parallel Self-Timed Adder". IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 23, NO. 1, JANUARY 2015.

- W. Liu, C. T. Gray, D. Fan, and W. J. Farlow, "A 250-MHz wave pipelined adder in 2-μm CMOS," IEEEJ.Solid-State Circuits, vol. 29 no. 9, pp. 1117–1128, Sep. 1994.

- 3. F.C. Cheng, S. H. Unger, and M. Theobald, "Self-timed carry lookahead adders," IEEE Trans. Comput., vol. 49, no. 7, pp. 659–672, Jul. 2000.

- 4. S.Nowick, "Design of a low-latency asynchronous adder using speculative completion," IEE Proc. Comput Digital Tech., vol. 143, no. 5, pp. 301–307, Sep. 1996.

- 5. M. Anis, S. Member, M. Allam, and M. Elmasry, "Impact of technology scaling on CMOS logic styles," IEEETrans. Circuits Syst., Analog Digital Signal Process., vol. 49, no. 8, pp. 577–588, Aug. 2002.

- Mohab H. Anis, Student Member, IEEE, Mohamed W. Allam, Member, IEEE, and asry, Fellow, IEEE, "Energy-Efficient Noise-Tolerant Dynamic Styles for Scaled-Down CMOS and MTCMOS Technologies," IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 10, NO. 2, APRIL 2002.

- 7. K.Venkata Siva Reddy, C.Venkataiah, Design of Adder in Multiple Logic Styles for Low Power VLSI", International Journal of Computer Trends and Technology, vol. 3, no.3, pp.476-481, 2012.

- Lixin Gao," High Performance Complementary PassTransistor Logic Full Adder", Proceedings of International Conference on Electronic & Mechanical Engineering and Information Technology, Harbin, China pp-4306-4309, August 2011.

- 9. N. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective. Reading, MA, USA: Addison-Wesley, 2005.

- 10. J.Sparsø and S.Furber, Principles of Asynchronous Circuit Design. Boston, MA, USA: Kluwer Academic, 2001.