## International Journal of Control Theory and Applications

ISSN: 0974-5572

© International Science Press

Volume 10 • Number 28 • 2017

# **State of Art Review of Various Control Methods for Cascade H-Bridge 5-Level Inverter to Mitigate Harmonics**

## V. Narasimhulu,\* D. V. Ashok Kumar\*\*, Ch. Sai Babu\*\*\*

\* Research Scholar, E.E.E Department, JNTUK, KAKINADA, A.P, India. E-Mail: narasimhapid@gmail.com

\*\* Professor of E.E.E & Dean Administration, RGMCET, Nandyal, Andhra Pradesh, India

\*\*\* Professor of E.E.E and the Registrar, JNTUK, Kakinada, Andhra Pradesh, India

*Abstract:* The modified Space Vector Pulse Width Modulation (Modified SVPWM) with triangular type multi carriers is proposed to control the switches for Cascade H-Bridge (CHB) 5-level inverter. The phase shift and level shift carriers are used in both Sinusoidal and modified SVPWM methods. The comparative harmonic analysis of modified SVPWM and sinusoidal PWM (SPWM) for CHB 5-level with various modulation indices is validated through simulation results.

Keywords: Cascade H-bridge; Phase shift; PD; POD; APOD; SPWM; Modified SVPWM and THD.

## I. INTRODUCTION

The higher level inverters are an important role in various applications. The CHB inverters are having more advantages when compare to all other multilevel inverters, because of its modularity. Various advantages and applications include motor drive; transmission and distribution are presented in [1]. The CHB inverter performance is high compared to all other multilevel inverter [2].

Various gate control methods are: phase shift and level shift methods are used to control the gate pulse of an IGBT device in CHB 5-level inverter [4]. The level shift PWM is preferred due to fewer harmonics compared to phase shift carrier gate control method [5]. The harmonic reduction concept for CHB inverters is presented in [6]. In this proposed work, the CHB 5-level inverter load voltage is discussed for different modulation methodologies. The RL load is considered for performance evaluation of both level and phase shift carrier based gate control methodologies.

## **II. CHB 5-LEVEL INVERTER**

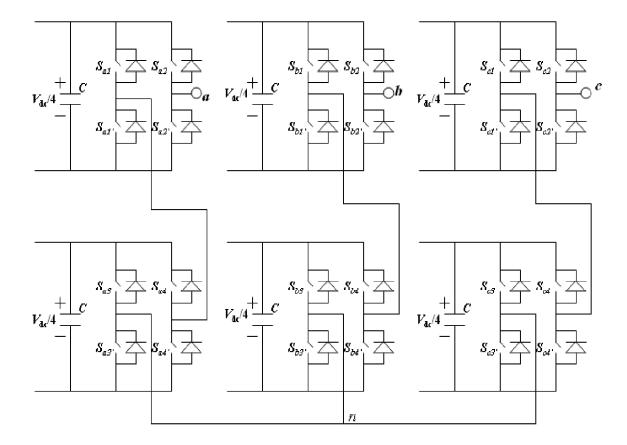

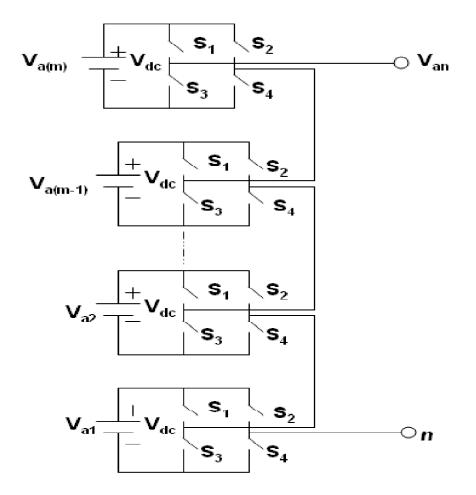

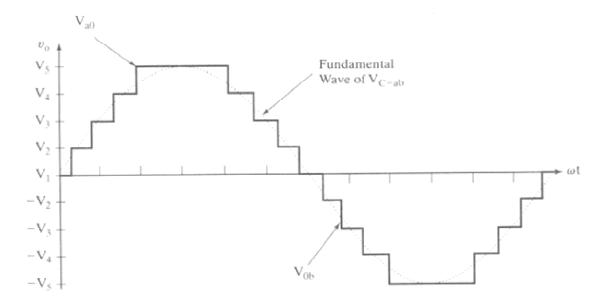

The schematic diagram of CHB 5-level inverter and m-level inverter is illustrated in Fig.1 and Fig.2. An equivalent 5-level load voltage is presented in Fig.3, which is  $v_{an} = v_{a1} + v_{a2} + v_{a3} + v_{a4}$ . The four switches of one H-Bridge is denoted as  $S_{a1}$ ,  $S_{a2}$ ,  $S_{a3}$ , and  $S_{a4}$ . Switching on  $S_1$  and  $S_4$  gives  $V_{a4} = +V_{dc}$ , likewise switching on  $S_2$  and switch  $S_3$

1

gives  $V_{a4} = -V_{dc}$ . By switching off all IGBTs yields Va4=0. If the  $V_{dcn}$  is the 'n' number of dc supplies, the RL load line-ground voltage level is m=  $V_{dcn}$ +1. Therefore, four DC supplies are required to operate a 5-level CHB inverter. Harmonics are reduced at different inverter level of waveform due to on/off control of an IGBT device angles during conduction.

The schematic diagram of CHB 5-level inverter and m-level inverter is illustrated in Fig.1 and Fig.2. An equivalent 5-level load voltage is presented in Fig.3, which is  $v_{an}=v_{a1}+v_{a2}+v_{a3}+v_{a4}$ . The four switches of one H-Bridge is denoted as  $S_{a1}$ ,  $S_{a2}$ ,  $S_{a3}$ , and  $S_{a4}$ . Switching on  $S_1$  and  $S_4$  gives  $V_{a4}=+V_{dc}$ , likewise switching on  $S_2$  and switch  $S_3$  gives  $V_{a4}=-V_{dc}$ . By switching off all IGBTs yields Va4=0. If the  $V_{dcn}$  is the 'n' number of dc supplies, the RL load line-ground voltage level is  $m=V_{dcn}+1$ . Therefore, four DC supplies are required to operate a 5-level CHB inverter. Harmonics are reduced at different inverter level of waveform due to on/off control of an IGBT device angles during conduction.

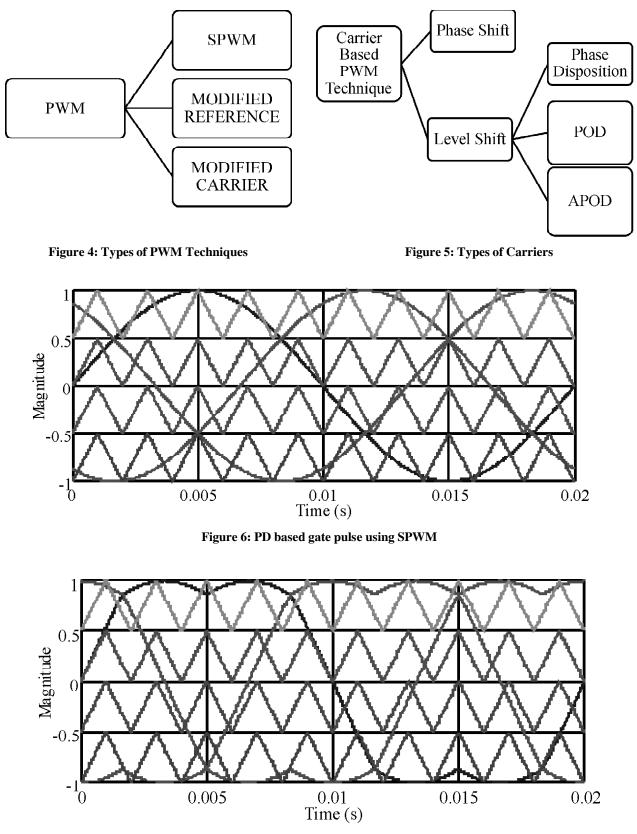

#### **III. ADVANCED PWM TECHNIQUES**

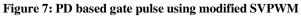

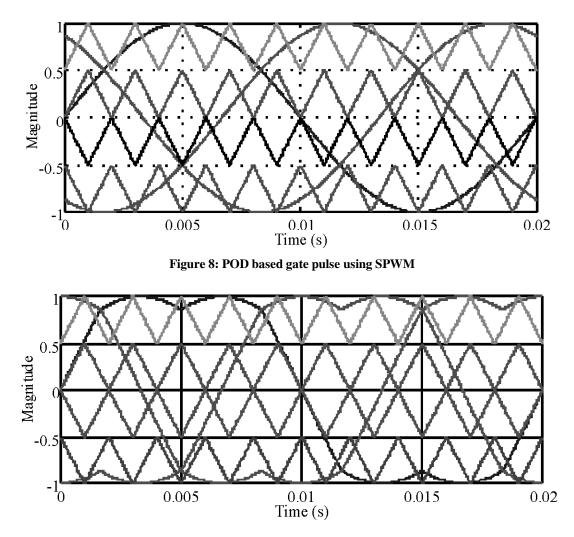

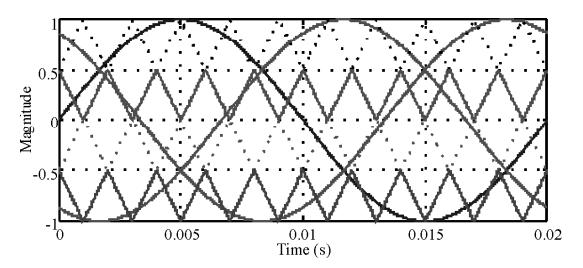

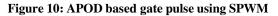

Various types of gate control techniques and the carriers are shown in Fig. 4 & Fig.5. The triangular carriers are chosen on the basis of the formula m-1, i.e 5-1=4 for the gate pulses of 5-level CHB inverter. Phase Disposition (PD) carriers are having the same in amplitude, frequency, and phases, but they are differ in DC offset to inhabit adjacent bands as shown in Fig 6, and Fig.7. Phase Opposition Disposition (POD) Carriers are having the same in magnitude and frequency but they are differing in phase and DC offset in Fig.8 & Fig.9. Alternative Phase Opposition Disposition (APOD) carriers are having the same magnitude and frequency but they are be different in their DC offset and phases as shown in Fig.10 and Fig.11.

Figure 1: 3-phase 3-leg 5-level CHB inverter [7], [8]

Figure 2: CHB m-level inverter [7], [8]

V. Narasimhulu, D. V. Ashok Kumar, Ch. Sai Babu

Figure 9: POD based gate pulse using modified SVPWM

International Journal of Control Theory and Applications

Figure 11: APOD based gate pulse using modified SVPWM

#### **IV. SIMULATION RESULT ANALYSIS**

#### 4.1. SPWM

In this Section, level shift and phase shift carriers is considered for result analysis. RL load parameters: are  $R=50\Omega$  and L=110mH. The DC voltage is 400V is applied. The switching frequency is 10 kHz.

#### (A) Phase Shift Carriers

Figure 12: Line-Line load Voltage and FFT spectrum Using phase shift carriers

#### (B) Level Shift Carriers

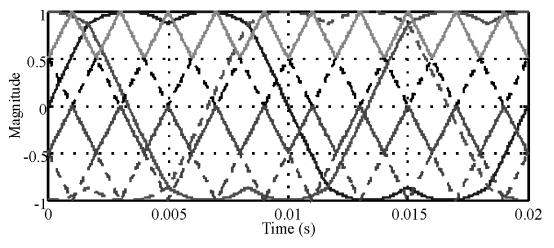

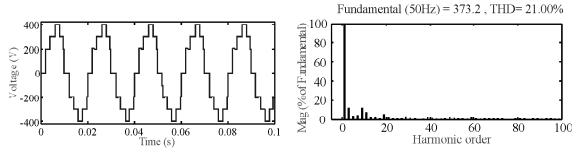

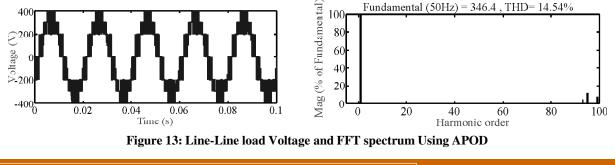

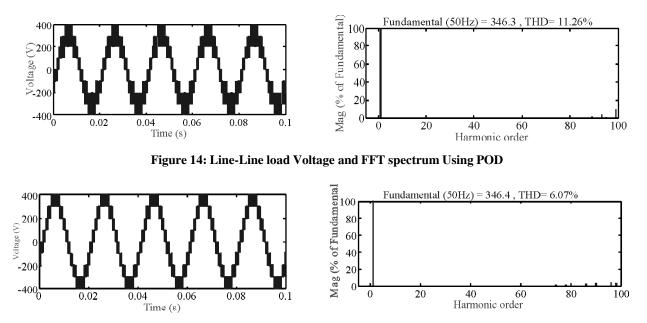

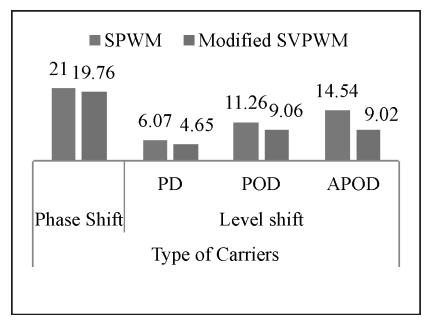

Fig.12 is the Line-Line load Voltage and FFT spectrum using phase shift carriers with total harmonic distortion is 21.00%. Fig.13, Fig.14 and Fig.15 is the Line-Line load Voltage and FFT spectrum using APOD, POD and PD triangular carriers with total harmonic distortion is 14.54%, 11.26% and 6.07% respectively using SPWM. The simulation results are presented in Table I.

Fig.15. Line-Line load Voltage and FFT spectrum Using PD

| Modulation index (M) | Type of Carriers |             |       |       |  |  |

|----------------------|------------------|-------------|-------|-------|--|--|

|                      | Phase Shift      | Level shift |       |       |  |  |

|                      |                  | PD          | POD   | APOD  |  |  |

| M=1                  | 21.00            | 6.07        | 11.26 | 14.54 |  |  |

| M=0.9                | 26.78            | 5.29        | 17.73 | 17.01 |  |  |

| M=0.8                | 33.48            | 8.31        | 22.06 | 16.97 |  |  |

| M=0.7                | 29.44            | 8.46        | 22.86 | 12.45 |  |  |

Table IThe % THD comparison of load voltage for SPWM

## 4.2. Modified SVPWM

Figure 16: Line-Line load Voltage and FFT spectrum Using phase shift carriers

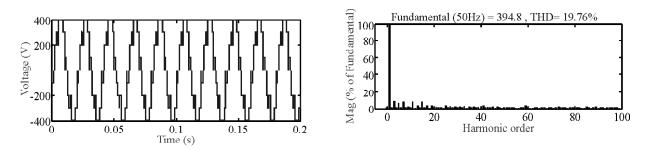

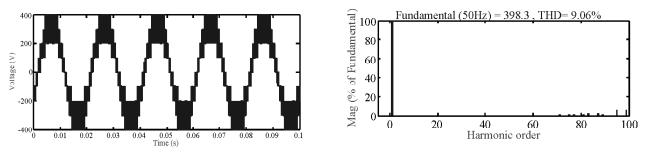

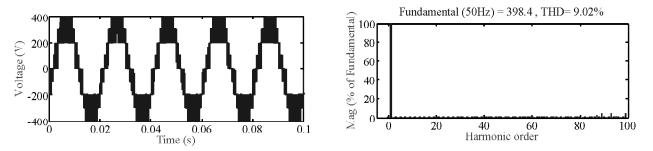

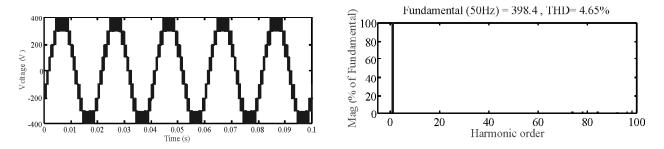

Fig.16 is Line-Line load Voltage and FFT spectrum using phase shift carriers with total harmonic distortion is 19.76%. Fig.17, Fig.18 and Fig.19 is Line-Line load Voltage and FFT spectrum using POD, APOD, and PD triangular carriers with total harmonic distortion is 9.06%, 9.02% and 4.65% respectively using modified SVPWM

technique. The simulation results are presented in Table II. The comparative illustration of SPWM and Modified SVPWM is shown in Fig. 20.

Figure 17: Line-Line load Voltage and FFT spectrum Using POD

Figure 18: Line-Line load Voltage and FFT spectrum Using APOD

Figure 19: Line-Line load Voltage and FFT spectrum Using PD

Table II

% THD comparison of load voltage for modified SVPWM

| Modulation index ( M) | Type of Carriers |             |       |       |  |  |

|-----------------------|------------------|-------------|-------|-------|--|--|

|                       | Phase Shift      | Level shift |       |       |  |  |

|                       |                  | PD          | POD   | APOD  |  |  |

| M=1                   | 19.76            | 4.65        | 9.06  | 9.02  |  |  |

| M=0.9                 | 27.25            | 3.46        | 15.66 | 15.62 |  |  |

| M=0.8                 | 32.41            | 5.57        | 21.01 | 21.03 |  |  |

| M=0.7                 | 36.65            | 5.23        | 21.36 | 21.37 |  |  |

State of Art Review of Various Control Methods for Cascade H-Bridge 5-Level Inverter to Mitigate Harmonics

Figure 20: An illustration of Total Harmonic Distortion using SPWM and Modified SVPWM

## V. CONCLUSION

In this paper, various Carrier-Based PWM techniques of PD, POD and APOD are analyzed. The simulation result analysis for line-line load voltage with harmonic spectrum is discussed. 5-level CHB inverter of modified reference with triangular carrier PWM technique have good FFT spectrum with THD (4.65%) when compared with modified PSPWM (19.76%).

## REFERENCES

- [1] R. Sastry Vedam, Mulukutla S. Sarma "power Quality VAR Compensation in Power Systems" CRC Press Taylor & Francis Group, 2009.

- [2] M. Odavic, et.al, "Multilevel Inverters: A survey of topologies, controls and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [3] F. Z. Peng and J. S. Lai, "Multilevel cascade voltage-source inverter with separate DC sources," U.S. Patent 5 642 275, Jun. 24, 1997.

- [4] L. Tolbert and T. G. Habetler, "Novel multilevel inverter carrier-based PWM method," IEEE Trans. Ind. Applicat., vol. 35, pp. 1098–1107, Sept./Oct. 1999.

- [5] V. G. Agelidis and M. Calais, "Application specific harmonic performance evaluation of multicarrier PWM techniques," in Proc. IEEE PESC'98, Fukuoka, Japan, May 1998, pp. 172–178.

- [6] Nima Yousefpoor, et.al, "THD Minimization Applied Directly on the Line-to-Line Voltage of Multilevel Inverters" IEEE Transactions on Industrial Electronics, Vol. 59, No. 1, January 2012.

- [7] M.H. Rashid, "Power Electronics Circuits devices, and Application' 3<sup>rd</sup> edition, Pearson/Prentice Hall, 2004.

- [8] Bin Wu, "High power converters and AC drives" IEEE Press, A John wiley & Sons inc., Publication.