# Analyzing the Effect of Voltage Variation in a Thin-Film Transistor with Silicon

Sakshi<sup>1</sup>, Sandeep Dhariwal<sup>2</sup> and Ravi Shankar Mishra<sup>3</sup>

#### ABSTRACT

In this paper, high-performance poly-Si TFT with  $ZrTiO_4$  as gate dielectric material under optimized MILC silicide material has been analyzed. The EOT of the dielectric use is 4.1 nm. The electrical performance of this setup attained a low value for threshold voltage of -2 V and a steep SS of 1.70E+00 V/dec. These properties thus obtained pose to be the best performance properties of the poly-Si TFT with high-K gate dielectric material that is ZTO.

IndexTerms: TFT, ZTO, MILC, EOT

#### 1. INTRODUCTION

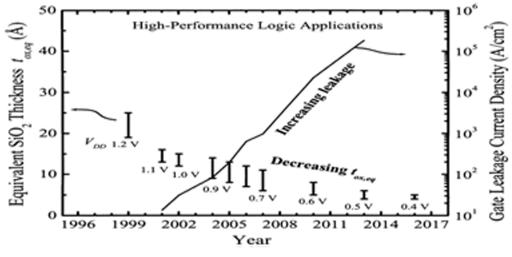

In VLSI, the topic of major concern is the methods that can be adopted to improve the performance and increase the miniaturization of the MOS devices. For the last forty years, the gate dielectric material being used is Silicon Dioxide since it provides a continuous improved performance as it is scaled down which also improves the performance of MOS device. This continuous scaling, for the last few years, has resulted in the continuous increase in the power dissipation which poses to be a serious issue [1-2]. The gate dielectric material, Silicon Dioxide, scaling has reached to a limit that further scaling will lead to an increase in the direct tunneling effect, power consumption, etc. [2-4]. Gate dielectric thickness of MOSFET device for the Scaling has been presented according to the prediction of ITRS in the following figure 1 [5]

It is clear from the roadmap that with the continuous scaling of the gate-dielectric material there is a continuous increase in the gate leakage currents, so to resolve this problem of leakage currents alternative

<sup>&</sup>lt;sup>1,2,3</sup> Lovely Professional University, Phagwara, India, Emails: manish.bansalbti@gmail.com, sandeep.19381@lpu.co.in, ravi.19053@lpu.co.in

dielectric materials with high dielectric constant are being investigated to find a proper replacement of Silicon Dioxide.

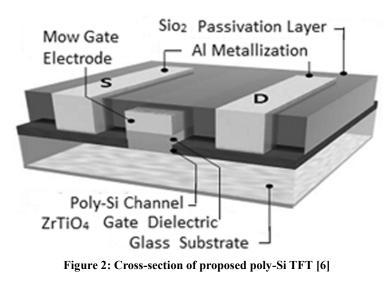

Thin-film transistor (TFT) is a type of Field Effect Transistor (FET) which has been widely employed in various displays as these provide high driving current. To overcome the limitations of poly-Si TFT with SPC channel and scaled Silicon Dioxide gate dielectric, metal- oxide gate dielectrics with high-k dielectric constants have been investigated. Some of them are HfO<sub>2</sub>, HfSiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, Pr<sub>2</sub>O<sub>3</sub>, LaAlO<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, Eu<sub>2</sub>O<sub>3</sub> and PrTiO<sub>4</sub>. All these candidates proved themselves unsuitable in one way or the other. The high-K dielectric material that can be used should have high dielectric constant, band-gap matching with poly-Si, and low cost elements. All these requirements have been obtained from  $ZrTiO_4$  (ZTO) as its dielectric constant is higher (50.5), band alignment is also in acceptable form and highly good thermal stability with poly-Si [6-8]. Figure 2 shows the proposed cross-section of poly-Si TFT with high-K gate dielectric material like ZTO [6].

## 2. EXPERIMENTAL WORK

The cross-sectional view of the poly-Si TFT with ZTO dielectric is being shown in the figure 2. For better performance, the optimization is done in two parts, first, by optimizing metal induced crystallized material and second, the dielectric optimization with ZTO. Initially, at a temperature of about 500 °C a 50-nm thick amorphous-Si is deposited by LPCVD. Sputtering is done to deposit 5-nm thick NiSi<sub>2</sub> nanoparticle seeds. Then annealing is done at temperature of about 550 °C by ambient H<sub>2</sub> for 2 hours for MILC process. In MILC, alpha silicon film layers are used for managing the Ni functionality with silicide seeds and crystallization method has been optimized. Alpha Si films are selected with thickness of 100-nm along with SiO<sub>2</sub> layer structure with 200nm thickness. This setup is simulated at temperature of 450 degree with low chemical vapor process with corning glass. Threshold voltage roll-off functionalities and electrical characteristics are tested with the proposed poly-Si TFT with ZTO material under optimized MILC silicide material.

## 3. RESULTS AND DISCUSSIONS

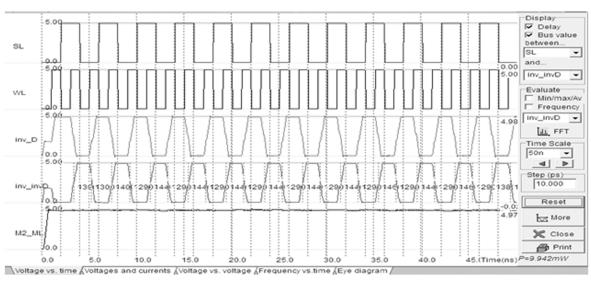

The simulations are done by using software Microwind3.1. The variation in length has been made with the values of 8, 10, and 15  $\mu$ m with a fixed width of 4 $\mu$ m. The variation in the threshold voltage roll-off and electrical characteristics has been studied on the basis of a) Voltage vs Voltage, b) Voltage vs Current, and c) Voltage vs Time. The voltage versus time simulation is done to obtain the transient analysis of the available signals. Here the simulations are done between the nodes SL and inv\_invD with SL and WL as two clocks or pulses provided to the transistor.

Figure 3: Voltage vs Time Curve

The results shown in the figure 3 show that the overall performance of the device has increased due to the decrease in the net delay at the output node.

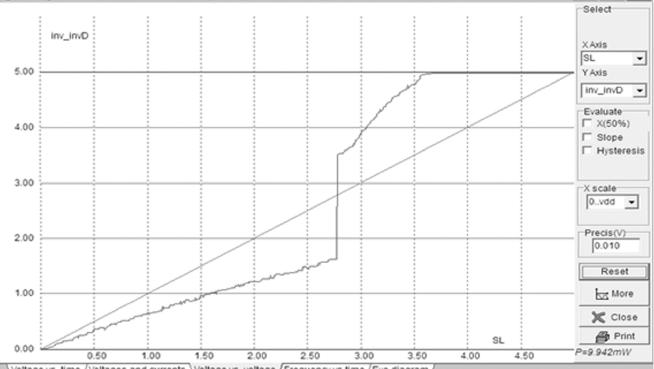

Voltage vs Voltage simulation is done to obtain the transfer characteristics of the selected nodes. In this mode, the inverter characteristics have been calculated and also the values of the stop node and start node from 0 to  $V_{\rm DD}$  are calculated.

The results shown in figure 4 depict that the total voltage obtained at the output node is much efficient. It depicts that the efficiency of the device has increased remarkably with low leakage and low power dissipation.

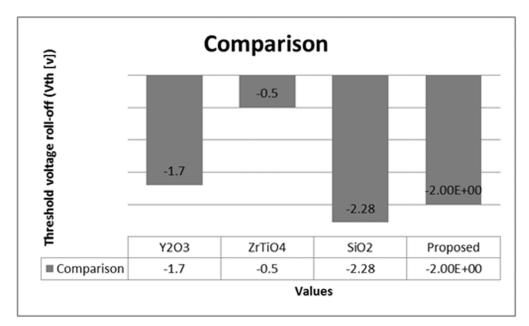

Further, the proposed results we have obtained are being compared with the existing results. From this comparison in figur 5, we have found that there is an increase in the threshold voltage roll-off in the

Voltage vs. time &Voltages and currents &Voltage vs. voltage & Frequency vs.time & Eve diagram /

Figure 5: Vth roll-off properties comparison

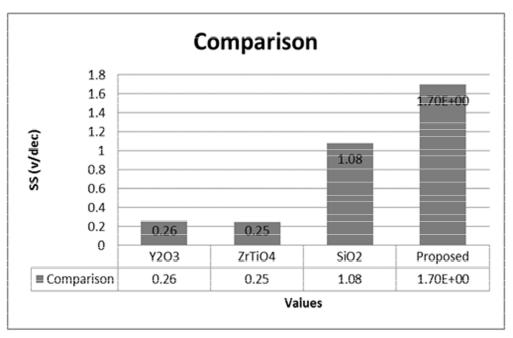

Figure 6: Electrical properties on steep comparison

proposed work from the earlier one. Hence the decrease in the leakage current and the power dissipation has been observed.

Figure 6 describes the comparison in the electrical properties on the basis of SS (V/dec). The graph shows the advancement in the SS of the proposed work. That is, subthreshold conduction is 1.7V per 10 times of the total drain current flowing through the device. In other words, the average subthreshold current has decreased resulting in the improvement in the performance of the MOS device.

#### 4. CONCLUSION

This paper is concluding performance of poly-Si TFT with high- K gate dielectric material ZTO under optimized MILC silicide material with a dielectric thickness of 4  $\mu$ m and channel length have been varied from 8, 10, and 15 $\mu$ m has been studied. This setup exhibited a low Vth of -2 V and steep SS of 1.70 V/dec.

27

The increase in the suppression of voltage roll-off has also been observed and was found very effective. These results obtained from the setup of poly-Si TFT with high-K gate dielectric material under optimized silicide material can thus be concluded as the best performance of the poly-Si TFT in comparison to the poly-Si TFT with high-K gate dielectrics used till now.

## ACKNOWLEDGMENT

I carried out my research work in Lovely Professional University Punjab and very thankful for helping me throughout the research work.

## REFERENCES

- [1] Paulo Francisco Butzen and Renato Perez Ribas, Leakage Current in Sub-Micrometer CMOS Gates, pp. 1.

- [2] G. Brezeanu, M. Brezeanu, F. Bernea, *High-K Dielectrics in Nano & Microelectronics*, Micro- and nanoengineering series, Vol 19, pp. 9-21, (November 2011).

- [3] P.S.Raja, R. Joseph Daniel, *Effect of gate dielectric on threshold voltage of Nanoscale MOSFETs*, International Journal of Engineering Research and Development, e-ISSN: 2278-067X, p-ISSN: 2278-800X, Volume 5, Issue 3, pp. 93-104, (December 2012).

- [4] Yee-Chia Yeo, Tsu-Jae King, and Chenming Hu, *MOSFET Gate Leakage Modeling and Selection Guide for Alternative Gate Dielectrics Based on Leakage Considerations*, IEEE Transactions on Electron Devices, Vol. 50, No. 4, (April 2003).

- [5] International Technology Roadmap for Semiconductors San Jose, CA, Semiconductor Industry Association (2001).

- [6] Jae Hyo Park, Gil Su Jang, Hyung Yoon Kim, Sol Kyu Lee, and Seung Ki Joo, *High-Peformance Poly-Si Thin-Film Tansistor With High-K ZrTiO<sub>4</sub> Gate Dielectric* IEEE Electroc Device Letters, Vol 36, No. 9, (September 2015).

- [7] M. Viticoli et al., Structural and dielectric properties of ZrTiO<sub>4</sub> and Zr<sub>0.8</sub>Sn<sub>0.2</sub>TiO<sub>4</sub> deposited by pulsed laser deposition, Mater. Sci. Eng. B, Vol. 118, nos. 1-3, pp. 87-91, (Apr. 2005).

- [8] C.Y. Wu et al., *Crystalline ZrTiO4 gated p-metal-oxide-semiconductor field effect transistors with sub-nm equivalent oxidethickness featuring good electrical characteristics and reliability*, Appl.Phys. Lett., vol. 106, no. 5, pp. 053508-1–053508-4, (Feb. 2015).