# A Novel Level Shifted Carrier PWM Technique for Neutral Point Stabilization of Five Level DCMLI

K. Narasimha Raju<sup>\*</sup>, Chandra Sekhar Obbu<sup>\*\*</sup> and G.D.G. Sai Kumar<sup>\*\*\*</sup>

*Abstract:* An existing problem with diode clamped multi-level inverter is having voltage oscillations at the neutral point. These oscillations cause uneven voltage sharing among the switching devices and increase the distortions in the output voltage. Inherent neutral point control is not possible i.e. they require extra components. However, these solutions are found not be practicable for many applications. A Novel Level Shifted Carrier based PWM technique has proposed for five level diode clamped multi-level inverter. In this the carrier shift will be done by measuring the Neutral-point voltage and current. The proposed convertor system will solve the voltage unbalance drawback of the conventional multilevel voltage-source converters, while not exploiting any extra voltage balance circuits or separate voltage sources. This technique has been verified by using MATLAB SIMULINK.

## 1. INTRODUCTION

The idea of multilevel converters has been introduced in 1975 [1]. Power electronic converters, particularly dc/ac PWM inverters are extending their vary of use in trade as a result of the supply reduced energy consumption, higher system potency, improved quality of product, smart maintenance, and so on. The most benefits of the multilevel inverters are Low THD, less EMI interference, higher bus utilization and low voltage stress [2]. The multi-level inverter is to synthesize a close to sinusoidal voltage from many levels of dc voltages. As range of levels will increase, the synthesized output waveform has a lot of steps, which provides a staircase wave that approaches a desired waveform. Also, as steps are added to wave, the harmonic distortion of the output wave decreases, because the range of voltage levels will increase. But multilevel converters do have some disadvantages [3]. Though the lower voltage rated switches is utilized in a multilevel converters, every switch needs a connected gate drive circuit. This might cause the general system to be more expensive and sophisticated. However the benefits of the multilevel converter have dominated its disadvantages.

As per literature there are three popular multilevel convertor structures reported, they're cascaded H-bridges convertor with separate dc sources, diode clamped, and flying capacitors [2]-[3]. However the diode clamped converter is usually used due to less dynamic voltage sharing problems, wonderful static equalization and low THD and dv/dt losses. However the drawback of the Diode clamped multilevel inverter is neutral point voltage instabilization i.e. a low-frequency voltage oscillation at the neutral point [1]. This is due to the difference in capacitor values because of manufacturing tolerances, Inconsistency in switching device characteristics, unbalanced three-phase operation [1]. Because of these oscillations in the neutral point, It causes an uneven voltage levels and hence increases output distortions, It also results in premature failure of switching devices. However, it's long been recognized that once a variety of levels larger than three is employed, capacitor voltage equalization is just accomplishable if the modulation index

<sup>\*</sup> Research scholar, Department of Electrical & Electronics Engineering, K.L University, Vaddeswaram, Guntur, India

<sup>\*\*</sup> Professor, Department of Electrical Engineering, K.L University, Vaddeswaram, Guntur, India

<sup>\*\*\*</sup> P.G Student, Department of Electrical & Electronics Engineering, K.L University, Vaddeswaram, Guntur, India

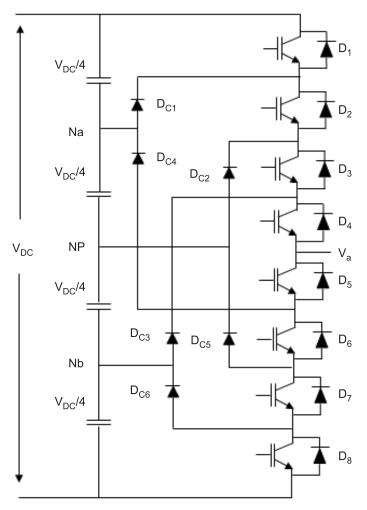

Figure 1: Five level structure of DCMLI

is restricted to max value of loads at 0.8 pf. For electrical converter applications, if the modulation indexes are beyond this limit, the middle capacitors tend to discharge and eventually the device converges to a 3 level [4]. This paper deals with the stabilization of the neutral voltage under varied loading conditions.

#### 2. EXISTING TECHNIQUE FOR NEUTRAL POINT STABILIZATION

Generally in the existing techniques the neutral point is rather stabilized by the carrier based pwm technique or the space vector pwm technique or both which is rather termed as the hybrid. For the neutral point stabilization using the carrier based pwm technique, the DC bias is added to the reference wave [5]-[6]. So in this case the dc bias added causes the shift of the reference wave thus on generate a median neutral current of the specified polarity to balance the capacitor voltages v1 and v2. As the output waveform reflects the reference wave, the DC bias or the DC shift causes the distortion in the output waveform which rather increases the THD of the output. Then in the space vector pwm technique, the neutral point voltage is stabilized by using the redundant states of the small vectors, as the small vectors majorly affect the neutral point voltage with less distortion, but the complexity of the logic for the generation of the waveforms and for the neutral voltage stabilization is the major drawback.

In the hybrid technique, the near vector and the non near vector strategies are used [9]-[10]. The nearest vector deals with the nearest three vectors where the neutral point is stabilized using the vectors in the

sector near the reference vector which is rather similar to carrier based pwm technique. In the non-nearest vector, the neutral point is stabilized using the vectors which are rather not near to the reference vector. These two techniques are the controlled by a threshold value. But the main drawback of this technique is that the logic is very complex to determine as the both Nearest Vectors and Non Nearest Vectors strategies are the types of the space vector PWM techniques. The voltage generation is done using the carrier based pulse width modulation technique [5] which is rather simpler and the neutral point voltage stabilization is done using the space vector pwm technique [7], which is rather the best way for the voltage generation and the neutral point voltage stabilization. The procedure deals with the switching in between the sine PWM technique and the space vector PWM technique [9]. The voltage equalization management theory for the multilevel "back-to-back" rectifier/inverter system is given. The strategy depends on coordination between rectifier and inverter switching angles to attain capacitance charge balance and at a similar time minimize the switch harmonics of each rectifier and electrical converter. The strategy differs from that given in [4] this a voltage-source management is implemented on each rectifier and inverter circuits.

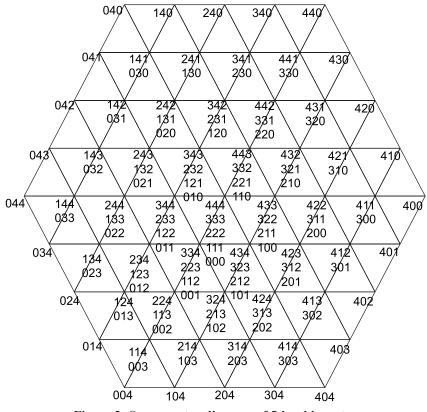

Figure 2: Space vector diagram of 5-level inverter

### 3. PROPOSED TECHNIQUE FOR NEUTRAL POINT STABILIZATION

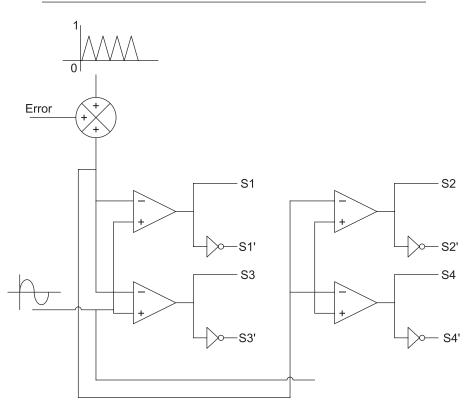

The existing techniques apply well for 3-level inverter, but fails for higher levels. The paper proposes a novel level shifted carrier PWM scheme for 5-level Diode clamped multilevel inverter. In the proposed technique neutral-point stabilization for five level diode clamped multilevel inverter by done by appropriately level shifting the carrier signal [9] shown in Figure 3(b). By shifting the width of the pulses change which results in delay in turn on and turn off the switches. This result in discharging the overcharged capacitor and charging of under charged capacitor will stabilize [11]. In the five level diode clamped multilevel

inverter there are four capacitors and hence three capacitor junctions i.e.  $N_a$ , NP (Neutral point),  $N_b$  as shown in Figure 1. Unlike the existing carrier based PWM techniques were reference is level shifted, As there is only single reference wave i.e. only one degree of freedom to control the various capacitor junction. This can mitigate the neutral point voltage oscillation. But the other two junctions are not at fixed levels as expected. This results in distorted output voltage. But in the proposed scheme as level shifting of carrier is done and there are 4 carriers, There are more degrees of freedom which leads to better stabilization of all the capacitor junctions. The main theme here involves the controlling of these three capacitor junction voltages Figure 2. For stabilizing the capacitor junctions voltages ( $V_{cn} - V_{cn} + 1$ ) connected to that junction are measured. Using these values the dc offset i.e. error to be added to the carrier signals of respective phase is decided by following the truth table shown below in Table.1.That error is given to all the carriers of respective phases i.e., when n = 1 for phase A, n = 2 for phase B, n = 3 for phase C.

| Table 1                                                     |

|-------------------------------------------------------------|

| Truth table to increment or decrement the value of <i>e</i> |

| for neutral-point voltage balancing                         |

| $Sign(V_{cn} - V_{cn+l})$ | $Sign(I_n)$ | Error(e) |

|---------------------------|-------------|----------|

| 0                         | _           | 0        |

| 1                         | 1           | -1       |

| 1                         | -1          | 1        |

| -1                        | 1           | 1        |

| -1                        | -1          | -1       |

Figure 2: Schematic for level shifting carrier PWM for Neutral point stabilization

#### 4. SIMULATION RESULTS

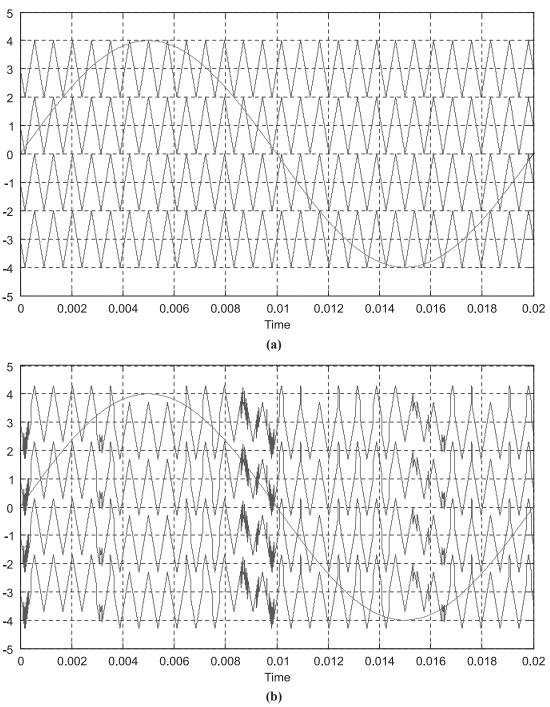

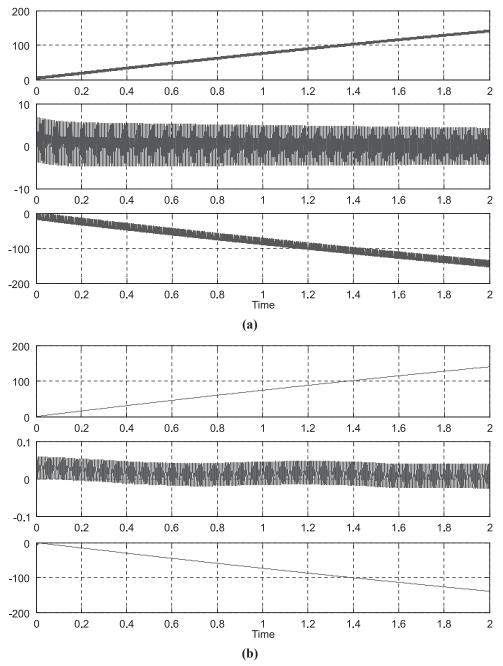

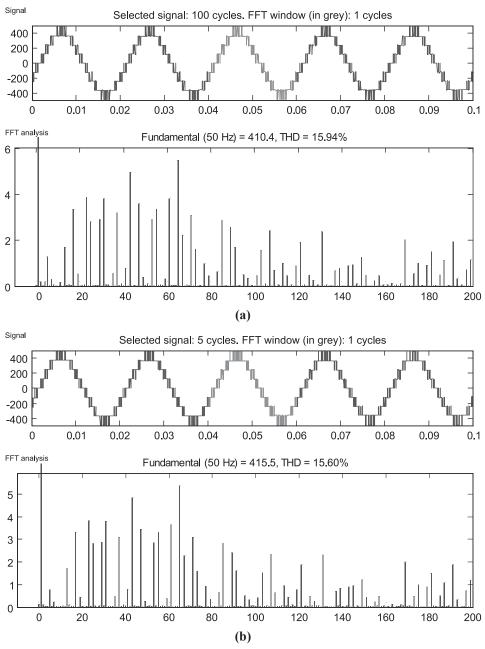

To appraise the performance of the proposed level shifted carrier PWM technique over the conventional PWM technique. The techniques applied to three phase five level DCMLI are simulated in the Matlab/Simulink. By choosing the parameters as  $V_s = 500$  V and R-L load is taken as 100  $\Omega$  and 10 mH. From the Figure 4, 5 observed reduction in the neutral point voltage and THD for the proposed and conventional sine pwm technique at unity power factor and Table 2 shows the Comparison of THD and Neutral Point Voltages for conventional and proposed techniques for different power factors.

Figure 3: Modulation technique for (a) Conventional Sine pwm and (b) Proposed Sine pwm

Figure 4: Neutral-point voltage for (a) Conventional Sine pwm and (b) Proposed Sine pwm

Table 2

Comparing the THD and NP Voltage of open loop and closed loop for different power factors

| Conventio    |                                  | echnique | Proposed Tec                     | Proposed Technique |  |

|--------------|----------------------------------|----------|----------------------------------|--------------------|--|

| Power Factor | Neutral-point Voltage<br>(Volts) | THD%     | Neutral-point Voltage<br>(Volts) | THD%               |  |

| Unity        | +5 to -5                         | 15.94    | +0.04 to -0.02                   | 15.60              |  |

| 0.8          | +40 to -40                       | 21.32    | +0.8 to -0.5                     | 16.38              |  |

| 0.6          | +50 to -50                       | 19.13    | +0.8 to -0.8                     | 15.86              |  |

| 0.4          | +40 to -40                       | 17.20    | +0.6 to -0.6                     | 15.56              |  |

| 0.2          | +25 to -25                       | 15.88    | +0.4 to -0.4                     | 15.43              |  |

Figure 5: THD for (a) Conventional Sine pwm and (b) Proposed Sine pwm

#### 5. CONCLUSION

A Novel level shifting carrier-based neutral point voltage balancing for a five-level Diode clamped multilevel inverter in combination with a closed-loop controller has been proposed in this paper. The proposed level shifting carrier PWM provides improved inverter performance in terms of reduced Total Harmonic Distortion (THD), harmonic profile, neutral point voltage and balanced dc link with near zero average Neutral point voltage.

#### References

- Jose Rodriguez, et. al, "A Survey on Neutral-Point-Clamped Inverters," *IEEE transactions on industrial electronics*, Vol. 57, No. 7, JULY 2010.

- 2. J. Rodriguez, et. al, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, Vol. 49, pp. 724-738, 2002.

- 3. J. S. Lai, et al, "Multilevel converters A new breed of power converters," *IEEE Trans. Ind. Applicant.*, Vol. 32, pp. 1098–1107, May/June 1996.

- 4. Z. Pan, et all, "Voltage Balancing Control of Diode-Clamped Multilevel Rectifier/Inverter Systems", *IEEE transactions* On Industry Applications, Vol -41. N° 6, Nov/Dec 2005, pp. 1668-1706.

- 5. Rangarajan M. Tallam, et. al, "A Carrier-Based PWM Scheme for Neutral-Point Voltage Balancing in Three-Level Inverters," *IEEE Trans. Ind. Appl.*, Vol. 41, No. 6, PP. 1734-1743, November/December 2005.

- 6. K. Narasimha Raju, et. al, "An effective carrier based PWM technique for neutral point voltage stabilization of three level inverter," in *IEEE conf. on Smart Electric Grid (ISEG)*, 2014.

- 7. Nikola Celanovic, et. al, "A Comprehensive Study of Neutral-Point Voltage Balancing Problem in Three-Level Neutral-Point-Clamped Voltage Source PWM Inverters," *IEEE Trans. Ind. Appl.*, Vol. 15, No. 2, PP. 242-249, March 2000.

- 8. Amit Kumar Gupta, et. al, "A Simple Space Vector PWM Scheme to Operate a Three-Level NPC Inverter at High Modulation Index Including Overmodulation Region, With Neutral Point Balancing," *IEEE Trans. Ind. Appl.*, Vol. 43, No. 3, PP. 751-760May/June 2007.

- 9. Jordi Zaragoza, et. al, "A Comprehensive Study of a Hybrid Modulation Technique for the Neutral-Point-Clamped Converter," *IEEE Trans. Ind. Appl.*, Vol. 56, No. 2, PP . 294-304, February 2009.

- Georgios I. Orfanoudakis, et. al, "Hybrid Modulation Strategies for Eliminating Low-Frequency Neutral-PointVoltage Oscillations in the Neutral-Point-Clamped Converter," *IEEE Trans. Pow. Elec.*, Vol. 28, No. 8, PP. 3653-3658, August 2013.

- 11. Narasimha Raju .K and M Ramamoorthy, "Hybrid modulation technique for neutral point clamped inverter to eliminate neutral point shift with minimum switching loss," in TENCON conf. 2015.

- 12. Rasoul Shalchi Alishah and Seyyed Hossein Hosseini "A New Multilevel Inverter Structure For High-PowerApplications using Multi-carrier PWM Switching Strategy" *International Journal of Power Electronics and Drive System (IJPEDS)* Vol. 6, No. 2, June 2015, pp. 318~325 ISSN: 2088-8694.

- 13. P. N. Tekwani, et. al, "A Dual Five-Level Inverter-Fed Induction Motor Drive With Common-Mode Voltage Elimination and DC-Link Capacitor Voltage Balancing Using Only the Switching-State Redundancy—Part I," *IEEE Trans. Ind. Appl.*, Vol. 54, No. 5, PP. 2600-2608, October 2007.

- 14. P. N. Tekwani, et. al, "A Dual Five-Level Inverter-Fed Induction Motor Drive With Common-Mode Voltage Elimination and DC-Link Capacitor Voltage Balancing Using Only the Switching-State Redundancy—Part II," *IEEE Trans. Ind. Appl.*, Vol. 54, No. 5, PP. 2609-2617, October 2007.

- 15. Chenchen Wang, Yongdong Li, "Analysis and Calculation of Zero-Sequence Voltage Considering Neutral-Point Potential Balancing in Three-Level NPC Converters," *IEEE Trans. Ind. Appl.*, Vol. 57, No. 7, PP. 2262-2271, July 2010.

- Joachim Holtz, Nikolaos Oikonomou, "Neutral Point Potential Balancing Algorithm at LowModulation Index for Three-Level Inverter Medium-Voltage Drives," *IEEE Trans. Ind. Appl.*, Vol. 43, No. 3, PP.761-768, May/June 2007.

- Till Boller, Joachim Holtz, Akshay K. Rathore, "Neutral-Point Potential Balancing UsingSynchronous Optimal Pulsewidth Modulation of Multilevel Inverters in Medium-Voltage High-Power AC Drives," *IEEE Trans. Ind. Appl.*, Vol. 50, No. 1, PP, 549-557, January/February 2014.

- 18. Bin Wu, IEEE Press, Wiley Interscience, "High-power converters and AC drives," 2006.