# Design and Implementation of Low Power Combinational Circuits using Reversible Logic

M. Janaki Rani<sup>1</sup>, S. Anandhi<sup>2</sup> and Manivannan<sup>3</sup>

#### ABSTRACT

Recent technology advancement in VLSI designs offer shrinking device dimensions and lead to exponential increase in circuit complexities. But this device scaling is limited by the power dissipation, which needs better power optimizations methods. The conventional digital circuits generate more heat due to the effect of logic gates which are irreversible in nature. Reversible logic is used to reduce the power dissipation that occurs in digital circuits by preventing the loss of information. Reversible Logic finds applications in Low Power CMOS designs, Quantum Computing, digital signal processing, communication, computer graphics, cryptography and Nanotechnology. The design of combinational logic circuits like adder, comparator, decoder, encoder, multiplexer and demultiplexer using reversible logic gates Feynman gate, Fredkin gate, Toffoli gate, Peres gate, HNG gate etc are discussed in this paper. The above circuits are simulated using Xilinx ISE Simulator 12.1.

Keywords: Low power, reversible logic, Feyman, Fredkin, Peres, combinational circuit

## 1. INTRODUCTION

The conventional combinational logic circuits designed using basic logic gates have energy loss due to the information bit lost during the operation. The total no of outputs generated is less than the total number of inputs applied in digital system and this is the major cause of the lowering of entropy and information loss of the overall digital system. The amount of energy loss for one bit of information loss in an irreversible gate was given by R. Landauer in 1961 [1]. Later in 1973 C. H. Bennett has shown that this energy loss can be minimized or even removed if the circuit is made up from the reversible logic gates [2]. Reversible circuit designing is gaining wide scope in the area of Quantum computing, Low power

CMOS design, Nanotechnology, Optical computing, Signal processing, Advanced computing etc due to its ability to design low loss or approximately loss less digital circuits.

A reversible logic gate is an n-input, n-output (denoted n\*n) logic device with one-to-one correspondence between the input and output. The important constraint present on the design of a reversible logic circuit using reversible logic gate is that fan-out is not allowed and loops are not permitted. A reversible circuit should be designed using minimum number of reversible gates. One key requirement to achieve optimization is that the designed circuit must produce minimum number of garbage outputs. The unutilized outputs from a reversible gate/circuit are called garbage outputs. Also they must use minimum number of constant inputs [3, 4]. Reversible logic circuits should have minimum quantum cost and must use a minimum logic depth or gate levels. Quantum cost refers to the cost of the circuit in terms of the cost of a primitive gate and gate level refers to the number of levels which are required to realize the given logic function.

<sup>&</sup>lt;sup>1,2</sup> Faculty, ECE Dept., Dr M.G.R Educational & Research Institute, Chennai, *Emails: janakiranimathi@gmail.com, anandhibalaji04@gmail.com*

<sup>&</sup>lt;sup>3</sup> Faculty, EEE Dept., Dr M.G.R. Educational & Research Institute, Chennai, Email: manivannank79@yahoo.com

This paper is organized as follows: Section 1 gives the introduction for reversible logic circuits. Section 2 gives some of the important reversible logic gates along with their logic functions. In Section 3 the design of combinational circuits full adder, full subtractor, one bit comparator, 2:4 decoder, der, 4:2 encoder, 4:1 multiplexer and 1:4 demultiplexer using reversible logic gates is discussed. Section 4 gives the simulation results of all the designs. Section 5 gives the comparison of all the designs and Section 6 gives the conclusion.

# 2. REVERSIBLE LOGIC GATES

In this section the reversible logic gates like Feynman gate [5], Peres gate [6], Toffoli gate [3] Fredkin gate [4], HNG gate, M gate, L gate and BJN gate are discussed.

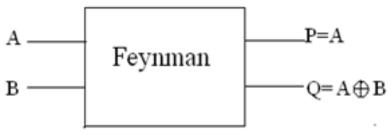

## 2.1. Feynman / CNOT Gate

Feynman gate is a 2\*2 gate and its circuit is shown in Fig. 1. It is also called as Controlled NOT and it is widely used for fan-out purposes. The inputs are A, B and outputs are P = A,  $Q = A \oplus \Box \Box B$  and its quantum cost is one.

Figure 1: Feynman gate-2\*2 gate

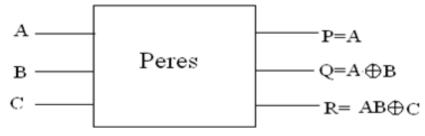

# 2.2. Peres Gate

Fig. 2 shows a Peres gate which is a 3\*3 gate having inputs (A, B, C) and outputs P = A,

$Q = A \oplus B$ ,  $R = AB \oplus C$  and its quantum cost is four.

Figure 2: Peres gate–3\*3 gate

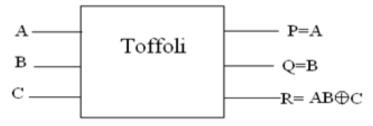

# 2.3. Toffoli Gate

Fig. 3 shows a Toffoli gate which is a 3\*3 gate with inputs (A, B, C) and outputs P = A,

Q = B,  $R = AB \oplus C$  and its quantum cost is five.

Figure 3: Toffoli gate-3\*3 gate

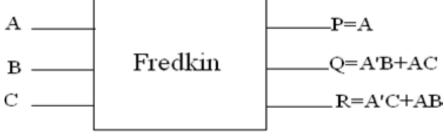

#### 2.4. Fredkin Gate

Fig. 4 shows a Fredkin gate which is a 3\*3 gate with inputs (A, B, C) and outputs P = A,

$Q = A \Box' B + AC$ , R = AB + A'C and its quantum cost is five.

Figure 4: Fredkin gate-3\*3 gate

#### 2.5. HNG Gate

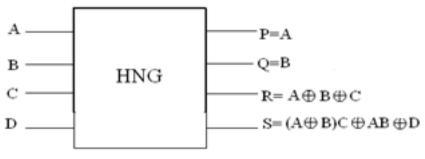

Fig. 5 shows a HNG gate which is a  $4 \times 4$  gate with inputs (A, B, C, D) and outputs P = A,

Q = B,  $R = A \oplus B \oplus C$ ,  $S = (A \oplus B)C \oplus AB \oplus D$  and its quantum cost is six[7]. It is used for designing ripple carry adders. It can produce both sum and carry in a single gate thus minimizing the garbage and gate counts.

Figure 5: HNG gate-4\*4 gate

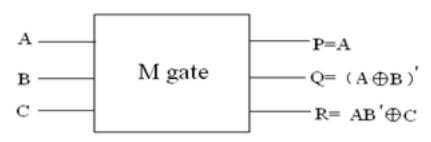

## 2.6. M Gate

Fig. 6 shows a M gate [8] which is a 3\*3 gate with inputs (A, B, C) and outputs P = A,

$Q = (A \oplus B)', R = AB' \oplus C.$

Figure 6: M gate-3\*3 gate

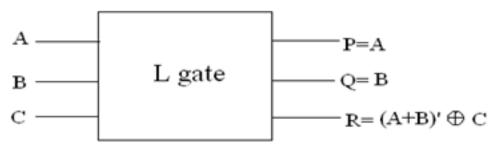

## 2.7. L Gate

Fig 7 shows a L gate [8] which is a 3\*3 gate with inputs (A, B, C) and outputs P = A,

$Q = B, R = (A+B)' \bullet "C.$

Figure 7: L gate-3\*3 gate

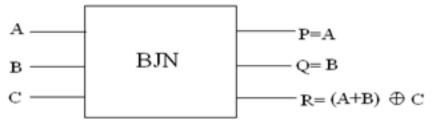

## 2.8. BJN Gate

Fig. 8 shows a BJN Gate which is a 3\*3 gate with inputs (A, B, C) and outputs P = A, Q = B,  $R = (A+B) \oplus C$ . It has quantum cost five.

Figure 8: BJN gate-3\*3 gate

## 3. REVERSIBLE LOGIC CIRCUITS

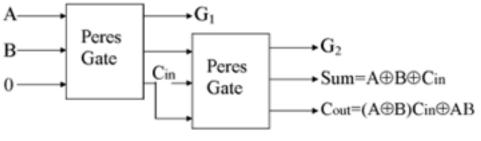

#### 3.1. Reversible Full adder

Full adder is the fundamental building block in many computational units. The full adder circuit's output is given by the following equations:

$$Sum = A \oplus B \oplus Cin$$

$$Cout = (A \oplus B)Cin \oplus AB$$

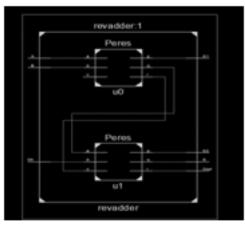

The reversible logic implementation of full-adder circuit is shown in Fig. 9. This reversible full adder circuit is realized using two 3\*3 Peres gates [9] and it is efficient in terms of gate count, garbage outputs and constant input than the existing counter parts.

Figure 9: Reversible full adder

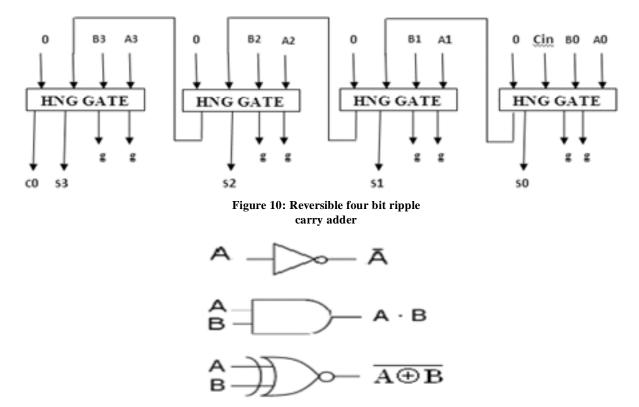

#### 3.2. Reversible Four bit adder

The block diagram of four bit ripple carry adder using HNG gates is shown in Fig 10.

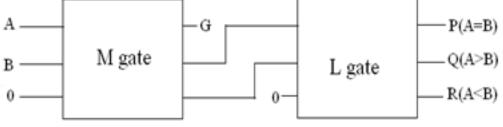

#### 3.3. Reversible one bit comparator

The conventional one-bit digital comparator [10], consists of two NOT gates, two AND gates and one NOR gate is shown in Fig.11. The truth table of one bit comparator is given in Table 1.

Figure 11: Irreversible gates for one bit comparator

|   | Inputs |      | Outputs                         |      |

|---|--------|------|---------------------------------|------|

| А | В      | FA>B | FA <b< th=""><th>FA=B</th></b<> | FA=B |

| 0 | 0      | 0    | 0                               | 1    |

| 0 | 1      | 0    | 1                               | 0    |

| 1 | 0      | 1    | 0                               | 0    |

| 1 | 1      | 0    | 0                               | 1    |

Table 1Truth Table of One Bit Comparator

Fig 12: Reversible one bit comparator

A reversible one bit comparator is designed using Mgate and L gate[8] as shown in Fig.12. It uses two constant inputs as logic'0' and has one garbage output.

#### 3.4. 2:4 Reversible Decoder

A decoder is a combinational circuit that converts binary information from n input lines to a maximum of  $2^{n}$  unique output lines. It is a multiple-input, multiple-output logic circuit that converts coded inputs into

Figure 13: Reversible 2:4 decoder

Table 2

Truth Table of 2:4 Ecoder with Enable Input

| Enable Input | Inj | puts |    | Outputs |    |    |  |  |

|--------------|-----|------|----|---------|----|----|--|--|

| S            | А   | В    | X0 | X1      | X2 | X3 |  |  |

| 0            | Х   | Х    | 0  | 0       | 0  | 0  |  |  |

| 1            | 0   | 0    | 1  | 0       | 0  | 0  |  |  |

| 1            | 0   | 1    | 0  | 1       | 0  | 0  |  |  |

| 1            | 1   | 0    | 0  | 0       | 1  | 0  |  |  |

| 1            | 1   | 1    | 0  | 0       | 0  | 1  |  |  |

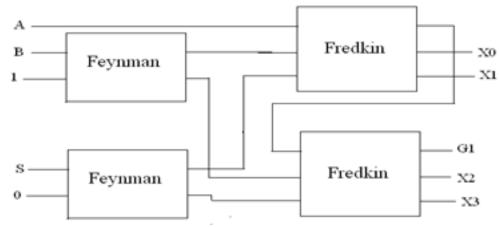

coded outputs, where the input and output codes are different. Enable inputs are required for the decoder to function, otherwise its outputs assume a single "disabled" output code word. Decoders are used in data multiplexing, seven segment display and memory address decoding. The truth table of decoder is given in Table II. The design of 2:4 decoder using Feynman gate and Fredkingate[11] is shown in Fig. 13 and it has one garbage output G1. The inputs are A, B and it has the enable input as S and the outputs are X0, X1, X2, X3.

## 3.5. A reversible 4:2 encoder

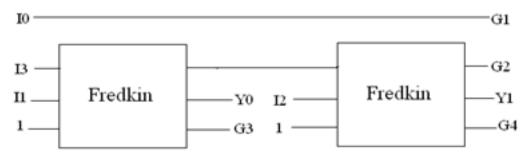

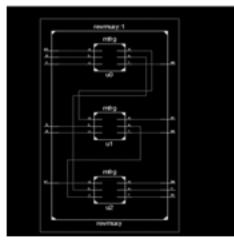

An encoder has 2<sup>n</sup> input lines and n output lines. The output lines generate a binary code corresponding to the input value. The truth table of encoder is given in Table III. The design of 4:2 encoder using using two Fredkin gates[12] is shown in Fig. 14. It has four inputs I0, I1, I2 I4 and two outputs Y1&Y2. It has four garbage outputs G1, G2, G3 and G4.

Figure 14: Reversible 4:2 encoder

|    | Table 3         Truth Table Of 4:2 Encoder |    |   |         |    |  |  |  |  |  |

|----|--------------------------------------------|----|---|---------|----|--|--|--|--|--|

|    | Inputs                                     |    |   | Outputs |    |  |  |  |  |  |

| I3 | I2                                         | I1 | Ю | Y1      | Y0 |  |  |  |  |  |

| 0  | 0                                          | 0  | 1 | 0       | 0  |  |  |  |  |  |

| 0  | 0                                          | 1  | 0 | 0       | 1  |  |  |  |  |  |

| 0  | 1                                          | 0  | 0 | 1       | 0  |  |  |  |  |  |

| 1  | 0                                          | 0  | 0 | 1       | 1  |  |  |  |  |  |

| 0  | 0                                          | 0  | 0 | Х       | х  |  |  |  |  |  |

| Table 3                    |  |

|----------------------------|--|

| Truth Table Of 4:2 Encoder |  |

|                            |  |

#### 3.6. A reversible 4:1 multiplexer

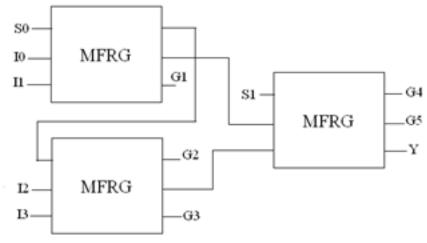

A multiplexer or MUX is a combinational logic circuit that has several inputs and only one output. MUX directs one of the inputs to its output line by using select lines. A multiplexer has 2<sup>n</sup> data inputs, n selection inputs and a single output. Selection input determines the input that should be connected to the output. The truth table of 4:1 multiplexer is given in Table IV.

Fig. 15 shows the block diagram of a 4:1 multiplexer using three modified Fredkin (MFRG) gates[13]. It has two select inputs S0, S1 and four data inputs I0, I1, I2, I3. The output is Y and this circuit has five garbage outputs G1, G2, G3, G4, G5.

Figure 15: Reversible 4:1 multiplexer

| Table 4                        |  |  |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|--|--|

| Truth Table of 4:1 Multiplexer |  |  |  |  |  |  |  |

| Select Inputs | Inj | outs | Output |    |   |   |  |

|---------------|-----|------|--------|----|---|---|--|

| <u>S1</u>     | SO  | I3   | I2     | I1 | Ю | Y |  |

| 0             | 0   | Х    | Х      | Х  | 0 | 0 |  |

| 0             | 0   | Х    | Х      | Х  | 1 | 1 |  |

| 0             | 1   | Х    | Х      | 0  | Х | 0 |  |

| 0             | 1   | Х    | Х      | 1  | Х | 1 |  |

| 1             | 0   | Х    | 0      | Х  | Х | 0 |  |

| 1             | 0   | Х    | 1      | Х  | Х | 1 |  |

| 1             | 1   | 0    | Х      | Х  | Х | 0 |  |

| 1             | 1   | 1    | х      | х  | Х | 1 |  |

## 3.7. A reversible 1:4 demultiplexer

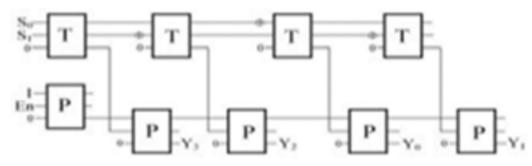

It is a digital logic circuit which performs inverse operation of the multiplexer. It has one input line Din and transmits it to one of  $2^n$  possible output lines. The selection of the specific output is controlled by the bit combination of n select inputs.

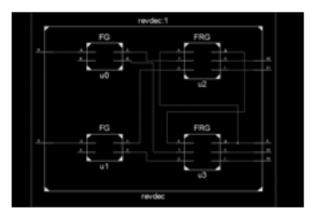

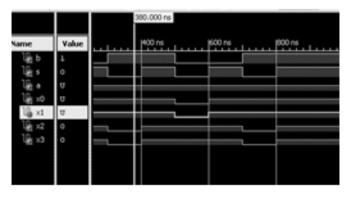

The truth table of 1:4 demultiplexer is given in Table V. Fig. 16 shows the block diagram of a 1:4 demultiplexer using Toffoli gates and Peres gates[14]. It has two select inputs S0, S1, one data input Din, enable input E and four outputs Yo, Y1, Y2, Y3. This circuit has nine garbage outputs.

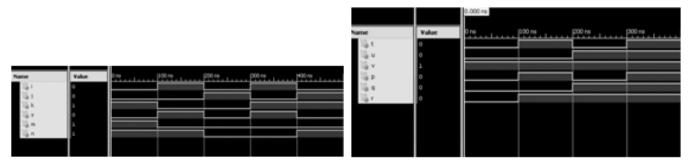

## 4. SIMULATION RESULTS

All the circuits are implemented using VHSIC hardware description language (VHDL). The simulation is done on Xilinx ISE 12.1 on Spartan 3 using target device: XC3S50-PQ208. The simulation waveform of

|              | Table V Truth Table Of 1:4 Demultiplexer |        |     |         |    |     |  |  |  |

|--------------|------------------------------------------|--------|-----|---------|----|-----|--|--|--|

| Enable input | Select                                   | Inputs |     | Outputs |    |     |  |  |  |

| E            | S1                                       | SO     | Y0  | Y1      | Y2 | Y3  |  |  |  |

| 1            | 0                                        | 0      | Din | 0       | 0  | 0   |  |  |  |

| 1            | 1                                        | 0      | 0   | Din     | 0  | 0   |  |  |  |

| 1            | 0                                        | 1      | 0   | 0       | 0  | Din |  |  |  |

| 1            | 1                                        | 1      | 0   | 0       | 0  | Din |  |  |  |

| 0            | Х                                        | Х      | 0   | 0       | 0  | 0   |  |  |  |

Fig. 16. Reversible 1:4 demultiplexer

|      |       |      |        |         |        | 342.000 ns |

|------|-------|------|--------|---------|--------|------------|

| ние  | Value | 0.04 | 100 ms | [200 ns | 200 ns |            |

| 16 a | 1     |      |        |         |        |            |

| 15 в | 1     |      |        | 1       |        |            |

| 16 p | 1     |      |        |         |        |            |

| 16 4 | 0     |      |        |         | L      |            |

|      |       |      |        |         |        |            |

|      |       |      |        |         |        |            |

Figure 17 (a): Output waveform of Feyman Gate

Figure 17 (c): Output waveform of Peres Gate

Figure 17 (b): Output waveform of Fredkin Gate

Figure 17 (d): Output waveform of MFRG Gate

Table 5 Table V Truth Table Of 1:4 Demultiplexer

Figure 17 (e): Output waveform of M Gate

Figure 18 (a): RTL view of reversible adder

Figure 19 (a): RTL view of reversible encoder

Figure 17 (f): Output waveform of L Gate

| Name     | Value | 100 ns | 150 ns | L . | 200 ns | 250 ns | p00 ns | 050 ns |

|----------|-------|--------|--------|-----|--------|--------|--------|--------|

| 18 e     | 0     |        |        |     |        |        | 1      |        |

| 1@ b     | 1     |        |        |     |        |        | t      |        |

| lig on   | 1     |        |        |     |        |        |        |        |

| liĝi gi  | 0     |        |        |     |        |        | 1      |        |

| 1ê 92    | 1     |        |        |     | L      |        |        |        |

| 16 +     | 0     |        |        |     |        |        |        |        |

| Tig cost | 1     |        |        |     |        |        | ţ      |        |

|          |       |        |        |     |        |        |        |        |

|          |       |        |        |     |        |        |        |        |

|          |       |        |        |     |        |        |        |        |

Figure 18 (b): Output waveforms of reversible adder

| 1     | Yakar | 258.44 | 07014 | 200 % | 053 % | 1800 14 | MO IN | 500 m |

|-------|-------|--------|-------|-------|-------|---------|-------|-------|

| ile a |       |        |       |       |       |         |       |       |

| 1.0   |       | -      |       |       |       | -       |       |       |

| 15 a  | 4     |        |       |       |       |         |       |       |

| 100   | 0     |        |       |       |       |         |       |       |

| 10.0  | 0     |        |       |       |       |         |       |       |

| 10.00 |       |        |       |       |       |         |       |       |

| 14.07 | 9     |        |       |       |       |         |       |       |

| 10.04 | •     |        |       |       |       |         |       |       |

| 10.11 |       |        |       |       |       |         |       |       |

| 10    | ÷ .   |        | _     |       |       |         |       |       |

|       |       |        |       |       |       |         |       |       |

| 1.0   | 1     |        |       |       |       |         |       |       |

Figure 19 (b): Output waveforms of reversible encoder

Feyman gate, Fredkin gate, Peres gate MFRG gate, M gate and L gate are shown in Fig. 17 a, b, c, d, e and f respectively. The RTL schematic and output waveforms for reversible adder, reversible encoder, reversible multiplexer and reversible decoder are shown in Fig. 18, Fig. 19, Fig. 20 and Fig. 21 respectively.

## 5. CONCLUSION

In this paper various reversible logics like Feyman gate, Fredkin gate, Peres gate, M gate, L gate and modified Fredkin gateMFRG are implemented using VHDL coding in Xilinx 12.1. Also the combinational

Figure 20 (a): RTL view of reversible multiplexer

Figure 21 (a): RTL view of reversible decoder

|        |      |     |        | <br>      |       |     |                    |

|--------|------|-----|--------|-----------|-------|-----|--------------------|

|        |      |     |        |           |       |     |                    |

| fame   | Take | 6 m | pilles | <br>200 m | 001-1 | HOL | 501 10 1 1 1 1 1 1 |

| là e   |      |     |        |           |       |     |                    |

| Táp et | 6    |     |        |           |       |     |                    |

|        |      |     |        |           |       |     |                    |

| là c   | •    |     |        |           |       |     |                    |

| la o   |      |     |        |           |       |     |                    |

| lig 4  |      |     |        |           |       |     |                    |

| lig of | 6    |     |        |           |       |     |                    |

| lag or | •    |     |        |           |       |     |                    |

| 18 ef  | •    |     |        |           |       |     |                    |

| 18 of  |      |     |        |           |       |     | _                  |

| 18 m   | •    |     |        |           | ļ     |     |                    |

| la τ   | •    |     |        |           | L     |     |                    |

|        |      |     |        |           |       |     |                    |

Figure 20 (b): Output waveforms of reversible multiplexer

Figure 21 (b): Output waveforms of reversible decoder

logic circuits like full adder, decoder, encoder, demultiplexer and multiplexer are are designed using the above mentioned reversible logic gates and their RTL schematic and simulation results are presented in this paper. These reversible circuits can be used for the design of ultra low power digital circuits, quantum computers and for applications in cryptography and nanotechnology.

#### REFERENCES

- [1] R. Landauer, "Irreversibility and Heat Generation in the Computational Process", IBM Journal of Research and Development, 5, pp.183-191, 1961.

- [2] C.H. Bennett, "Logical Reversibility of Computation", IBMJ. Research and Development, pp. 525-532, November 1973.

- [3] T. Toffoli., "Reversible Computing", Tech memo MIT/LCS/TM-151, MIT Lab for Computer Science 1980.

- [4] E. Fredkin and T. Toffoli, "Conservative logic," Int'l J. TheoreticalPhysics, Vol. 21, pp. 219–253, 1982.

- [5] R. Feynman, "Quantum Mechanical Computers," Optics News, Vol. 11, pp. 11–20, 1985.

- [6] Peres, "Reversible Logic and Quantum Computers", Physical review A, 32:3266-3276, 1985.

- [7] Himanshu. Thapliyal, K.P. Jacob, Majidhaghparast & Keivan Navi Design of High speed low power Reversible Logic BCD Adder Using HNG gate IEEE Transactions on VLSI Systems, March 2013.

- [8] Madhina Basha, V.N. Lakshmana Kumar, "Transistor Implementation of Reversible Comparator Circuit Using Low Power Technique", International Journal of Computer Science and Information Technologies, Vol. 3, No. 3, 2012, pp. 4447–4452.

- [9] Md. Saiful Islam and Md. Rafiqul Islam, "Minimization of Reversible Adder Circuits", Asian Journal of Information Technology, Vol. 4, No. 12, pp. 1146-1151, 2005.

- [10] A. N. Nagamani, H. V. Jayashree, H. R. Bhagyalakshmi, "Novel LowPower Comparator Design using Reversible Logic Gates" Indian Journal of computer Science and Engineering, Vol. 2, No. 4 Aug. Sep. 2011.

- [11] Lafifa Jamal, Md. Masbaul Alam, Hafiz Md. HasanBabu, "An efficient approach to design a reversible control unit of a processor" Sustainable Computing: Informatics and Systems 3 (2013) 286–294.

- [12] Neeta Pandey, Nalin Dadhich, Mohd. Zubair Talha, "Realization of 2:4 reversible decoder and its applications", International Conference on Signal Processing and Integrated Networks (SPIN).IEEE,2014.

- [13] AshimaMalhotra, Charanjit Singh, Amandeep Singh, "Efficient Design of Reversible Multiplexers with Low Quantum Cost and Power Consumption", International Journal of Emerging Technology and Advanced Engineering, Vol. 4, Issue 7, July 2014, pp. 518-523

- [14] Y. Syamala1 and A.V.N. Tilak, "Synthesis of Multiplexer and Demultiplexer Circuits using Reversible Logic", Int. J. of Recent Trends in Engineering and Technology, Vol. 4, No. 3, Nov. 2010.