# Modified Hybrid PWM Technique For Neutral Point Stabilization of Five Level Diode Clamped Inverter

K. Narasimharaju\*, O. Chandrasekhar\*\* and G. Padmasri\*\*\*

#### ABSTRACT

An intrinsic problem with diode clamped multi-level inverter is fluctuations or simply called unbalance of voltage at neutral point. This voltage fluctuations can cause uneven voltage sharing among the switching devices. Sometimes may cause failure and increases harmonic component in the output waveform. This problem is normally mitigated by closed loop control of neutral point voltage. There are many mitigation methods well established in literature to balance the neutral point voltage using conventional SPWM and space vector PWM techniques. But these techniques has drawbacks like low frequency ripples at the neutral point voltage i.e. With the combination of both SPWM and SVPWM techniques to the fullest for achieving efficient voltage balance at the neutral point by providing quality output for 5 level diode-clamped multi level inverter for any type of load. MATLAB-SIMULINK will be used to develop this technique.

*Keywords:* Diode clamped multi level inverter (dcmli), sinusoidal pulse width modulation (spwm), space vector pulse width modulation(svpwm), near vector(NV)

#### 1. INTRODUCTION

For the most part, diode-clamped multi level inverters (DCMLI) are using for the high power/ voltage applications. As compared with a two-level inverter, it has the accompanying preferences: 1) gives higher quality output; 2) it works at higher ac-voltage levels and minimize or even dispose the need of interface transformer; 3) decrease switching losses. In spite of its merits for high-voltage applications, [1] it has a drawback that neutral point voltage unbalance at its dc-side capacitors. The voltage-drift occurrence will decays the output waveform, ineffective operation DCMLI and also cause failure of the switches in DCMLI. Thus, there is requirement of equal voltage division between dc capacitors. The occurrence of voltage-drift across dc capacitors of a three level DCMLI has been greatly researched and categorized as SPWM,SHE and SVPWM. In all these modulating techniques linear controlling, direct torque controlling and predictive controlled methods were used. Recently some hybrid techniques were developed.

These hybrid techniques uses the combination of near vector and non-near vector techniques, which is going to nullify the drawback of both nearest vector techniques and non near-vector techniques. NV techniques eliminate neutral point voltage ripple for a certain range of load power angle  $\emptyset$  and converter modulation index m. Non-near vector strategies can eliminate neutral point voltage ripple but at the cost of high switching steps it causes high switching frequency when compared to nearest vector strategies. So for the effective control the neutral point unbalance and to decreases the switching losses of DCMLI, all this strategies were investigated extensively.

<sup>\*</sup> Associate Professor, Dept.of Electrical and ElectronicsEngineering, K L University, Vaddeswaram, India, *Email:* narasimharaju\_eee@kluniversity.in

<sup>\*\*</sup> Head of the Dept. of Electrical and Electronics Engineering, K L University, Vaddeswaram, India, Email: sekharobbu@kluniversity.in

Despite a wide range of applications that have been reported in the technical literature for a five-level diode clamped multi level inverter [5], but its capacitor-voltage-unbalance phenomenon has not been comprehensively analyzed. For five level DCI, it include more number of components and complexity of control circuit [6], [7] increases. A detailed study of five-level DCI will be projected in this project and focused on different approach called modified hybrid PWM technique, in order to balance the voltage unbalance phenomenon of five level DCI.

To overcome the neutral point voltage drift phenomena, this proposed technique gives efficient result at different power factors compared to normal sinusoidal pulse width modulation.

The rest of paper follows as: Section 2, Deals with literature review. Section 3 demonstrates the proposed system model and proposed techniques. Section 4 Discusses experimental results. Section 5 presents the conclusions and future enhancement.

#### 2. LITERATURE REVIEW

Selective harmonic elimination technique [1] was used and it is able to eliminate lower order harmonics which is below thirteenth order at 25 hz of load frequency. But practically it is complex to solve equations. Carrier based pulse width modulation technique is very popular. It is developed by comparing reference wave with 4 carrier waves but this technique is good at low modulation index. Space vector modulation technique has redundant states which is used to balance the neutral point voltage [2][3]. But the modulation technique is quite complex and also switching losses increases. To reduce the complexity of space vector modulation some more work was done in papers [4][5][6].

#### 3. 5 LEVEL DIODE CLAMPED INVERTER

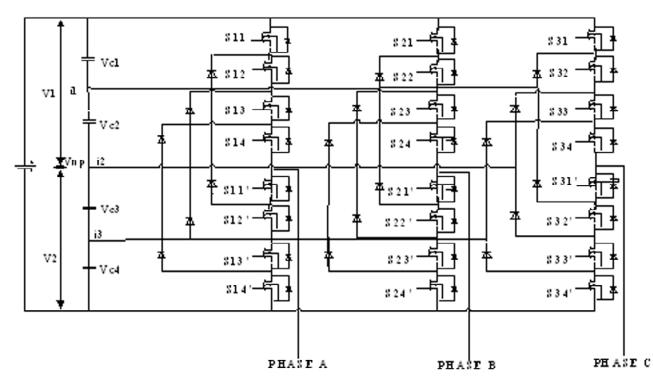

Figure 1 shows that the simplified circuit diagram of a five level diode clamped inverter. A diode clamped multi level inverter consist of (m-1) capacitors on the dc side and 2(m-1)switches for each leg. The table 1 describes the voltage level and their respective switching states. State condition 1 means the switch is on

Figure1: 5 level diode clamped inverter

| Table 1         5 level switching states, Switches(S), Mode(M) |     |     |     |     |      |      |      |      |                      |

|----------------------------------------------------------------|-----|-----|-----|-----|------|------|------|------|----------------------|

| S<br>M                                                         | S11 | S12 | S13 | S14 | S11' | S12' | S13' | S14' | Voltage<br>magnitude |

| 4                                                              | 1   | 1   | 1   | 1   | 0    | 0    | 0    | 0    | $+V_{dc}/2$          |

| 3                                                              | 0   | 1   | 1   | 1   | 1    | 0    | 0    | 0    | $+V_{dc}^{dc}/4$     |

| 2                                                              | 0   | 0   | 1   | 1   | 1    | 1    | 0    | 0    | 0                    |

| 1                                                              | 0   | 0   | 0   | 1   | 1    | 1    | 1    | 0    | -V <sub>dc</sub> /4  |

| 0                                                              | 0   | 0   | 0   | 0   | 1    | 1    | 1    | 1    | -V <sub>dc</sub> /2  |

and 0 means the switch is off. It should be noticed that each switch is turned on only once per cycle and there are four complementary switch pairs in each phase.

These pairs of one leg of inverter are(s11, s11'), (s12, s12'), (s13, s13'), (s14, s14'). If one of the complementary switch pair is on and the other of same pair must be off. The operating states of the switches and voltage magnitudes of the diode clamped inverter is shown in Table 1. Switching state "4" denotes that the upper four switches in leg A are on and the inverter terminal voltage  $v_{Anp}$ , which is the voltage at terminal A with respect to the neutral point np, is  $+V_{dc}/2$ , whereas "3" indicates that upper four switches but not first switch conduct, leading to  $v_{Anp} = +V_{dc}/4$ . Switching state "2" signifies that the inner four switches are on and  $v_{Az}$  is clamped to zero through the clamping diodes. Depending on the direction of load Switching state "1" signifies that the inner four switches but not last switch is on and  $v_{Anp} = -V_{dc}/4$  and Switching state "0" signifies that the inner four switches are on and  $v_{Anp} = -V_{dc}/2$ .

#### 3.1. 5-Level Space Vector

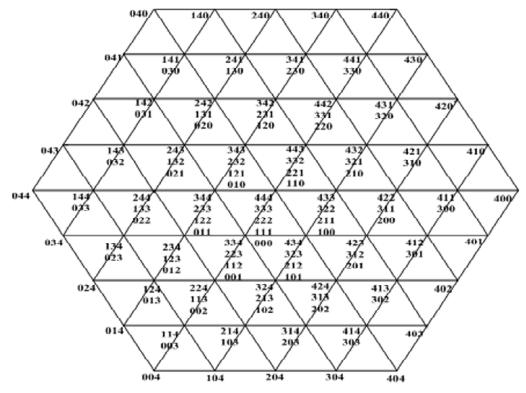

There are 125 switching states for the 5 level SVPWM as shown in Figure 2, for the 5 level there are more redundancy states which is defining as more switching states gives the same output voltage, and these

Figure 2: 5 level space vector diagram

redundant states are using for stabilization of the neutral point voltage unbalance. Inner hexagon states named as small vectors which is shown below figure has four redundancy states for each sector.

### 3.2. Proposed Technique

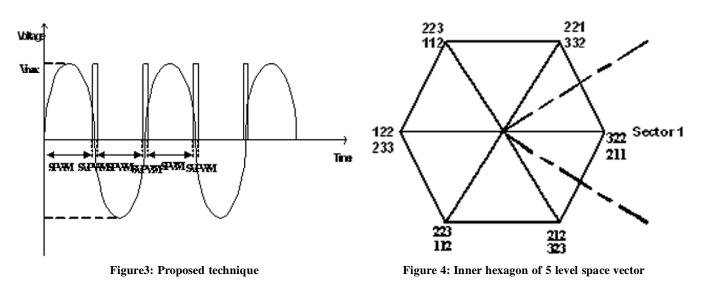

Combination of sinusoidal pulse width modulation and space vector modulation will be used, specifically SPWM will be used to operate the diode camped converter and SVPWM will be used at zero crossings of every phase voltage waves to stabilize the neutral point voltage at the same time to effect less distortion on output as shown in Figure 3.

Considering the direction of phase currents how these states effecting the neutral point and also considering less switching losses in view, two switching states per sector is taken into operation those which are effecting neutral point by phase current per sector is shown in Table 2.

Table 2

Voltage, Current and Power states being considered

| sector | $V_1 - V_2$          | Neutral point current $(i_{np})$ | $Power(V_1-V_2)^* (i_{np})$ |

|--------|----------------------|----------------------------------|-----------------------------|

| 1      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

| 2      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

| 3      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

| 4      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

| 5      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

| 6      | +ve or -ve+ve or -ve | +ve or -ve+ve or -ve             | +ve or -ve+ve or -ve        |

#### 3.3. Algorithm

- 1. When the phase voltage wave crosses zero the space vector technique gets activated

- 2. First the sector is determined in which the reference voltage is.

- 3. The difference of the capacitor voltages used in the inverter and the neutral current measurements are taken.

- 4. Then the neutral power is calculated.

- 5. The direction of the neutral power is taken into consideration.

6. Then according to the direction of the neutral power direction, the vectors are taken into consideration as shown in the table 2.

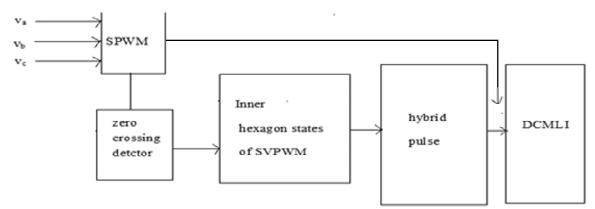

## 3.4. Block Diagram

Figure 5:Implementation of proposed technique

## 4. RESULTANDDISCUSSION

## 4.1. ExperimentalSetup

The proposed technique has been implemented using MATLAB/Simulink.Heresimulink models of conventional and proposed technique were developed using power system tool box and commonly used tool boxes.

## 4.2. Result

In this paper the neutral point voltage oscillations of five level inverter controlled by conventional sinusoidal PWM technique and the proposed modified hybrid PWM technique are compared for different power

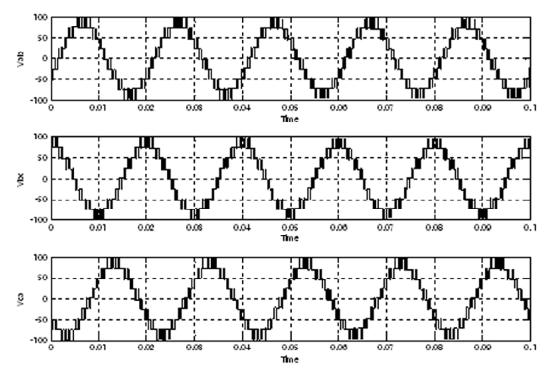

Figure 6: Output voltage of 5 level diode clamped inverter with proposed technique

factors. The supply voltage is considered to be 1000V and the capacitor values taken are 4mf. Figure 6 shows the output voltage of the five level inverter for the proposed technique. It can be observed that multilevels are equally spaced which demonstrates the equality of capacitor voltages.

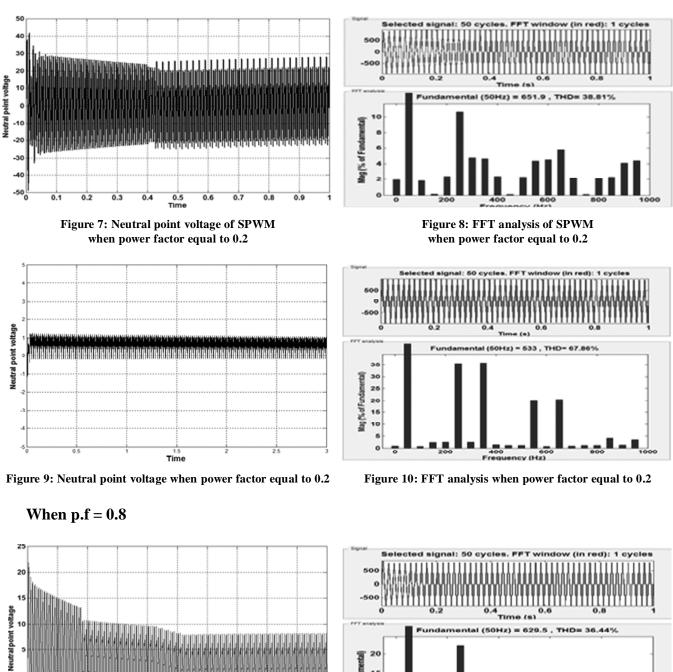

The figures 7-10 witness the reduction in the neutral point voltage for the proposed technique compared with the conventional sinePWM technique with a magnitude of about 50.8V It can be observed from Table 3.

When p.f. = 0.2

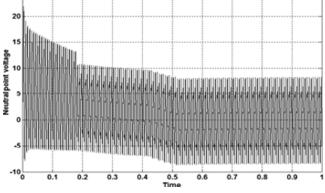

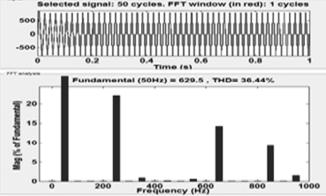

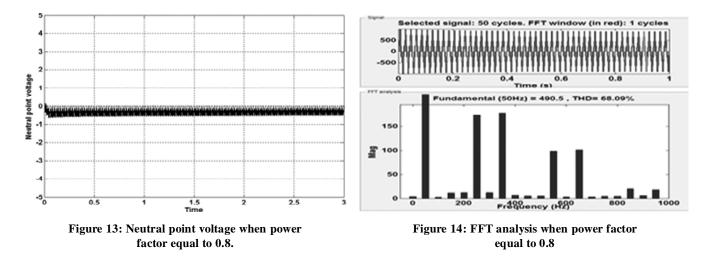

Figure 11: Neutral point voltage of SPWM when power factor equal to 0.8

Figure 12: FFT analysis of SPWM when power factor equal to 0.8

The figures 11-14 witness the reduction in the neutral point voltage for the proposed technique compared with the conventional sinePWM technique with a magnitude of about2.2V. It can be observed from Table 3.

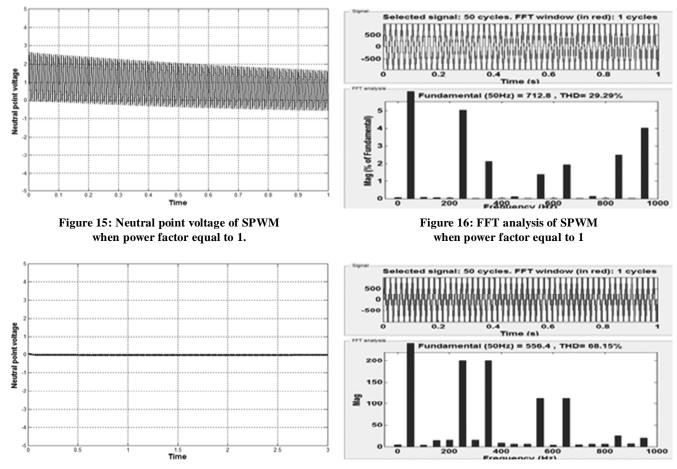

#### When **p.f.** = 1

The figures 11-14 witness the reduction in the neutral point voltage for the proposed technique compared with the conventional sinePWM technique with a magnitude of about 16V. It can be observed from Table 3.

Figure 17: Neutral point voltage, when power factor equal to 1.

Figure 18: FFT analysis, when power factor equal to 1

| Table 3           Variation of neutral point voltage and total harmonic distortion, Total harmonic distortion (THD) |             |                    |                     |                                  |                                    |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|-------------|--------------------|---------------------|----------------------------------|------------------------------------|--|--|--|

| S.NO                                                                                                                | Powerfactor | •/• THD<br>in SPWM | •/• THD<br>inhybrid | Neutral Point<br>Voltage in SPWM | Neutral Point<br>Voltage in hybrid |  |  |  |

| 1                                                                                                                   | 0.2         | 38.81              | 67.38               | 52                               | 1.2                                |  |  |  |

| 2                                                                                                                   | 0.4         | 38.42              | 68.11               | 45                               | 1 to -1                            |  |  |  |

| 3                                                                                                                   | 0.6         | 38.8               | 68.03               | 35                               | -1                                 |  |  |  |

| 4                                                                                                                   | 0.8         | 36.44              | 68.09               | 16                               | -0.5                               |  |  |  |

| 5                                                                                                                   | 1           | 29.29              | 68.12               | 2.5                              | 0.3                                |  |  |  |

The Table 3 shows the results obtained for p.f. = 0.2, 0.4, 0.6, 0.8 and 1. But the Figures are presented for p.f. = 0.2, 0.8 and 1.

## 5. CONCLUSION

The proposed technique is verified at different load power factors, it is observed that neutral point voltage balanced effectively but the total harmonic distortion increased. This technique makes use of redundant states in five level inverter thereby it simple mentation is quite easy when compared to other techniques.

#### REFFERENCES

- [1] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clampe PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [2] J. Pou, D. Boroyevich, and R. Pindado, "New feed forward space-vector PWM method to obtain balanced AC output voltages in a three-level neutral-point-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 1026-1034, Oct. 2002.

- [3] K. Gupta and M. Khambadkone, "A simple space vector PWM scheme to operate a three-level NPC inverter at high modulation index including overmodulation region, with neutral point balancing," *IEEE Trans. Ind.Appl.*, vol. 43, no. 3, pp. 751-760, May/Jun. 2007.

- [4] Georgios I. Orfanoudakis, Michael A. Yuratich, and Suleiman M. Sharkh Hybrid Modulation Strategies for Eliminating Low-Frequency Neutral-Point Voltage Oscillations in the Neutral-Point-Clamped Converter *Student Member, IEEE, IEEE transactions on power electronics*, vol. 28, no. 8, August 2013.

- [5] Rangarajan M. Tallam, A Carrier-Based PWM Scheme for Neutral-Point Voltage Balancing in Three-Level Inverters *Member, IEEE*, Rajendra Naik, *Member, IEEE*, and Thomas A. Nondahl, *Fellow, IEEE IEEE transactions on industry applications*, vol. 41, no. 6, november/december 2005.

- [6] Maryam Saeedifard, Analysis and Control of DC-Capacitor-Voltage-Drift Phenomenon of a Passive Front-End Five-Level Converter, *IEEE*, Reza Iravani, *Fellow, IEEE*, and Josep Pou, *Member, IEEE IEEE transactions on industrial electronics*, vol. 54, no. 6, December 2007.

- [7] Nikola Celanovic, *Student Member, IEEE*, and Dushan Boroyevich, *Member*A Comprehensive Study of Neutral-Point Voltage Balancing Problem in Three-Level Neutral-Point-Clamped Voltage Source PWM Inverters, *IEEE transactions on power electronics*, vol. 15, no. 2, March 2000.

- [8] Jose Rodriguez, Senior Member, IEEE, Steffen Bernet, Member, IEEE, Peter K. Steimer, Fellow, IEEE, and Ignacio E. Lizama A Survey on Neutral-Point-Clamped Inverters IEEE transactions on industrial electronics, vol. 57, no. 7, July 2010.

- [9] Jordi Zaragoza, Student Member, IEEE, Josep Pou, Member, IEEE, Salvador Ceballos, Student Member, IEEE, Eider Robles, Pedro Ibáñez, Member, IEEE, and Jose Luis VillateA Comprehensive Study of a Hybrid Modulation Technique for the Neutral-Point-Clamped Converter IEEE transactions on industrial electronics, vol. 56, no. 2, February 2009.