# Performance of Statcom Based on 84 Pulse Voltage Source Converter Configuration Using Multi Level DC Voltage Reinjection

T. Sruthi\* K. Sravanthi\*\* and K. Durga Syam Prasad\*\*\*

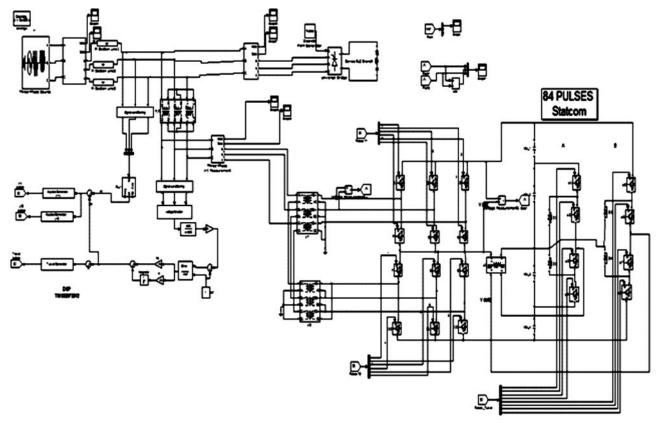

*Abstract :* This paper proposes a new configuration of 84-pulse voltage source converter composed of 12-pulse VSC, in conjunction with an asymmetric single phase 7-level converter with an injection transformer, this configuration or this arrangement is designed where the reduction of voltages will be seen with the VSC output's total harmonic distortion allowing it to be used in the especial applications or as the FACTS devices. The operational feasibility of proposed system was verified by the computer simulations with MATLAB/ SIMULINK. And the proposed strategy allows saving in the number of employed switches.

Keywords : Custom power, FACTS devices, Multipulse converters, StatCom, Voltage source converters.

# **1. INTRODUCTION**

The Static Synchronous Compensator (STATCOM) is one of the most useful FACTS devices, Since it can synthesize the reactive power from small storing elements [1].When it s operated with in the linear region, it is seen by the system as synchronous voltage source [2,3].By regulation of the StatCom's output voltage magnitude when these are operated with in the linear region it seen by the system as synchronous voltage magnitude is regulated then there will be an exchange between the device and the transmission system which may controlled and improves the power system profile [4, 5, 6, 7].

The STATCOM shows more effective on the fundamental sine wave at the frequencies that are multiples of the fundamental one. During this process there should be a special care because it can prevent the entire system without entering any unwanted harmonic issues. The voltage source converters are basically classified as three feasible strategies which is to assemble a VSC they are:

- 1. The multi-pulse

- 2. The multi-level

- 3. The pulse width modulation (PWM)

The In the VSC's output voltage should need some strong efforts, By this method or by this process the construction of the circuit and the usage of switches will be more and the task to perform will become very difficult, because of the use of more number of gating signals. So that we can't able to get rid of the formation of large chain of capacitors .A strategy to build an 84-pulse equivalent output voltage waveform, which employs a 12-pulse along with an 8-level reinjection converter is presented in[10].

<sup>\*</sup> PG Student, Vignan's Institute of Engineering for Women, Duvvada, Visakhapatnam

<sup>\*\*</sup> Assistant Professor, Vignan's Institute of Information Technology, Duvvada, Visakhapatnam.

<sup>\*\*\*</sup> Associate Professor, Vignan's Institute of Engineering for Women, Duvvada, Visakhapatnam

However the cost will be extra to build an 84-pulse need 26 extra switch devices and 7 DC voltage sources. So, to overcome this difficulty there is another method which is (MLVR)-Multilevel voltage reinjection H-bridge conversion which acts as the another remedy or option to generate the 84-pulse. The proposed strategy will constitutes the reduction of cost which was the main aspect to design the circuit. According to the current technology the voltage is generally be higher than the switches and diodes ratings in order with the high voltage applications [11].

# 2. 84-PULSE VSC TOPOLOGY

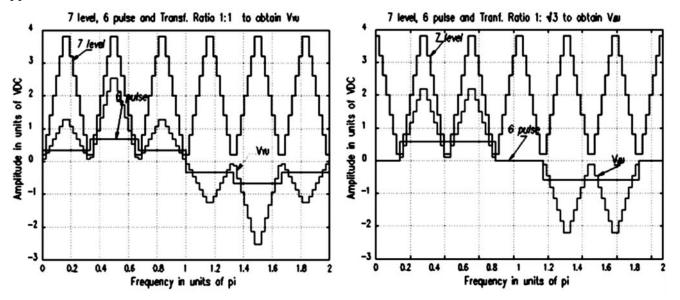

Several methods have been investigated to increase the number of pulse's in the multi-pulse converter's output. The simplest method is by increasing number of 6-pulse converters and the transformers.4 sixpulses converters results in 24-pulse, 8 six-pulse converter results in 48-pulses operation. The harmonic cancellation will be carried out by the arrangement of transformer secondary windings. The drawback of this method is large size and high cost due to the increased number of bridges and transformers. To overcome such difficulty, an auxiliary circuit in the DC link side has been proposed for reinjection[12]. Such topology results through modifying the DC input on the conventional double bridge 12-pulses shunt converters through a multi-level auxilary circuit with an injection transformer[13]. An asymmetric 7-level array for the auxiliary circuit is used as reinjection scheme is implemented in this paper, shows in Fig, 1. The conventional double bridge 12-pulse operation is placed by the connection of two identical three-phase bridges to three-phase transformers in parallel VSC configuration. In each branch the 6-pulse converter must have 120° displacement between them. The upper switch conducts while the lower switch is open and vice versawhich is equal to 180° voltage source operation [14]. The firing sequence of both converters should be considered as 30°. The transformers turns ratio's are 1:1 and 1: $\sqrt{3}$  on YY and Y $\Delta$  transformers, DC pulses are injected through three-phase bridges neutral point spreading an effect of pulse is attained. The auxiliary circuit is common for all the phases will reduces the number of extra components.

The complete configuration of pulse multiplication is explained detailed in [9,10,12,15,16,21] in fig.1 explains about auxiliary seven-level inverter used as a reinjection circuit. The seven-level inverter output voltage is applied to feed the 12-pulse converter while these application a special care should be taken without injecting negative voltage into  $V_{y}$  or  $V_{\Delta}$ . The inclusion of the injection transformer between both arrays are noticed. So, therefore the voltages at the six-pulses converter inputs can be regulated and adjusted the injection voltage  $U_{i}$  by

$$V_{\rm v} = V_{\rm DC} + U_i \tag{1}$$

$$V_{\Delta} = V_{DC} - U_i \tag{2}$$

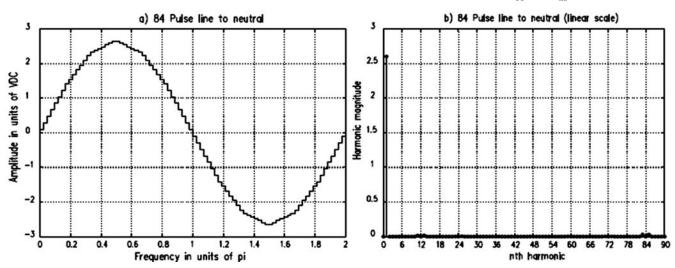

The injection voltage is determined by the seven-level inverter switching pattern and the injection transformer turns ratio. By Using voltages  $V_y$  and  $V_{\Delta}$  as inputs to the six-pulse converters,  $V_y$  And  $V_{\Delta}$  are the input voltages to the six-pulse converters load to the formation of cleaner VSC's output. Fig .2 Exhibits the followed strategy to build  $V_{yU}$  or  $V_{\Delta U}$  as the interaction of the seven-level output and the corresponding six-pulse signals. Through the 1:1 ratio for the YY TRANSFORMER,1: 3 for the Y $\Delta$  TRANSFORMER, and adding their corresponding output signals, 84-pulse line-to-neutral  $V_U$  emerges by adding these two output signals correspondingly. The spectrum is shown in fig. 3*b*, illustrated on a linear scale, it was seen in fig. 4 is displayed  $V_U$  is a odd symmetric signal, therefore the Fourier's even terms are zero. Thus,

$$V_{U}(t) = \sum_{n=1}^{\infty} V_{U_{2n-1}} \sin((2n-1)\omega t)$$

(3)

$$V_{U2n-1} = \frac{4V}{3\pi(2n-1)} (A_{2n-1} + aB_{2n-1})$$

(4)

$$A_{2n-1} = 2 + 2\cos\left(\frac{1}{3}\pi(2n-1)\right) + 2\sqrt{3}\cos\left(\frac{1}{6}\pi(2n-1)\right)$$

(5)

$$B_{2n-1} = \sum_{i=0}^{20} \operatorname{coeffi} \cos\left(\frac{i}{42}\pi(2n-1)\right)$$

(6)

Where

Fig. 1. 84-pulse StatCom structure.

# 3. MODELLING OF VSC BASED STATCOM

**Basic Operating Principles of STATCOM**

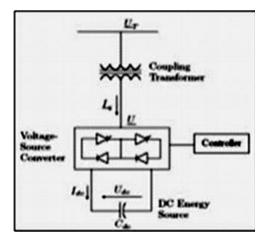

Fig. 2. Basic Statcom Structure.

The STATCOM is connected to the power system at a PCC (point of common coupling), through a step-up coupling transformer, in which there is a trouble with the voltage -quality. The PCC is known as the terminal for terminal voltage is which is UT. All required voltages and currents are measured and are fed into the controller to be compared with the commands. The controller then performs feedback control and outputs a set of switching signals (firing angle) to drive the main semiconductor switches of the power converter accordingly to either increase the voltage or to decrease it accordingly. A STATCOM is a controlled reactive-power source. It provides voltage support by generating or absorbing reactive power at the point of common coupling without the need of large external reactors or capacitor banks.

## 3.1. Voltage Source Converters (VSC)

A voltage-source converter is a power electronic device, which can generate a sinusoidal voltage with any required magnitude, frequency and phase angle. Voltage source converters are widely used in adjustable-speed drives, but can also be used to mitigate voltage dips. The VSC is used to either completely replace the voltage or to inject the 'missing voltage'. The 'missing voltage' is the difference between the nominal voltage and the actual. The converter is normally based on some kind of energy storage, which will supply the converter with a DC voltage. The solid-state electronics in the converter is then switched to get the desired output voltage. Normally the VSC is not only used for voltage dip mitigation, but also for other power quality issues, *e.g.* flicker and harmonics. The voltage source-converter or inverter (VSC or VSI) is the building block of a STATCOM and other FACTS devices. A very simple inverter produces a square voltage waveform as it switches the direct voltage source on and off. The basic objective of a VSI is to produce a sinusoidal AC voltage with minimal harmonic distortion from a DC voltage. Three basic techniques are used for reducing harmonics in the converter output voltage. Harmonic neutralization using magnetic coupling (multi-pulse converter configurations. Harmonic reduction using multi-level converter configurations and the pulse-width modulation (PWM).

### 3.2. Multi-Pulse Converter Configuration

Multi-pulse operation is achieved, by connecting identical three-phase bridges, to transformers which have outputs that are phase-displaced with respect to one another. Star and delta-connected windings have a relative 300 phase shift and a 6-pulse converter bridge connected to each transformer will give an overall 12-pulse operation eliminating 5th and 7th harmonics. This principle can be extended to 24- and48-pulse operation summing at the primary windings the transformed outputs of several 6-pulse converters (4 for 24-pulse and 8 for 48-pulse operation). The harmonic cancellation is carried out into the transformer secondary winding Multi-pulse staircase voltage waveform

## 3.3. Multi-Level Inverter Configuration

The multi-level inverters synthesize a staircase voltage wave, from several levels of DC voltage sources, obtained from capacitor voltage source. As the number of levels increases, the synthesized staircase wave approaches the sinusoidal wave resulting in reduced harmonic distortion. a single-phase five level voltage source inverter, this converter is more complex and requires the DC voltage source to be split or centre-tapped in order to provide a zero voltage reference. Five-level voltage source inverter The fundamental magnitude and the harmonic spectrum are controlled varying the switching angles,  $\alpha$ . The fundamental voltage component can also be changed by keeping  $\alpha$  constant and changing VDC. Alternative forms of multilevel converters is the chain circuit in which several converter bridges, each with its own source capacitor, are connected in series.

## 3.4. Pulse Width Modulation (PWM)

In multi-pulse and multi-level converters, there is only one turn-on, turn-off per device per cycle. An- other approach is to have multiple pulses per half-cycle, and then vary the width of the pulses to vary the amplitude of the AC voltage. The pulse width modulation (PWM) technique is commonly employed to generate high quality output waveforms by relatively low power converter used in variable frequency AC motor drives and distribution applications. With this technique, the output of each converter pole is switched several times during a fundamental cycle between the positive and negative terminals of the DC PWM requires a considerable increase in the number switch operations (high switching frequency);thereby it generally increases the switching losses of the converter. However, the always increasing switching frequency of modern solid-state power switches could made possible the use of PWM in high power applications.

Fig. 4. Mixing seven-level, six-pulse signals, and transformer's ratios to attain.  $V_{yu}$  and  $V_{Au}$ .

Fig. 5(*a*). 84-pulse line-to-neutral output voltage and 5 (*b*) harmonic content minimize the total harmonic istortionTHD), which is defined by [9, 17].

$$THD^{VU} = \sqrt{\frac{\sum_{n=2}^{\infty} V_{Un}^2}{V_{U1}^2}}$$

$$(8)$$

The minimization of THD yields the parameter *a*. In this paper such estimation has been made through MATLAB for a value n = 7200, with increments of a = 0.0001. With these parameters, the minimum THD becomes 2.358% with a = 0.5609, value employed in previous figures. According to the IEEE Std. 519, the distortion limits indicate that the allowed THD voltage is 10% in dedicated systems, 5% ingeneral systems, and 3% for special applications as hospitals and airports [17]. Table 1 presents the voltage's

minimum THD generated by several multi-pulse configurations. Through our proposition, the resultant TH allows its use even in applications with stringent quality requirements; it exhibits less dependence to variations in the transformer's turn ratio a, which can have a variation until +/-12.5% to reach a maximum THD lower than 3%.

# 4. OPEN LOOP STATCOM STRUCTURE

The connection of the improved VSC to the system requires aspects to be considered. This section deals with such details within an open loop context.

# 4.1. Phase-Locked-Loop (PLL)

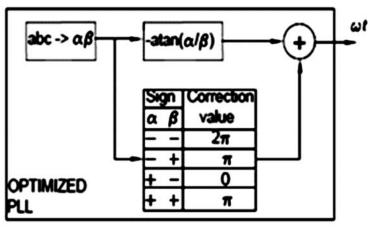

The connection of the improved VSC to the system requires aspects to be considered. This section deals with such details within an open loop context. 3.1 Phase-Locked-Loop (PLL) The Synchronizing Circuit is responsible for determining the system frequency and the phase-angle of the controlled AC bus fundamental positive sequence voltage [18]. The Phase Locked-Loop (PLL) utilizes the Stationary Reference Frame in order to reduce the computational cost, and helps to improve the system's dynamic performance [19]. The digital PLL is an algorithm able to detect the phase of the fundamental voltage, through the synchronization of the output signal to the frequency and phase of the input one, without requiring a zero crossing subroutine at the input voltage, or to generate an internal reference signal for the input current [20]. The proposed strategy employs a

Fig. 3. Optimized PLL scheme.

# 4.2. Six-Pulse Generator

The second block is the six-pulse generator, responsible for generating the pulse sequence to fire the three-phase IGBT array. It consists of an array of six-pulse spaced 60° each other. The IGBT will operate at full 180° for the on period and 180° for the off period. Any disturbance on the frequency will be captured by the synchronizing block, preventing malfunctioning. The falling border in the synchronizing block output signal is added to a series of six 60° spaced signals. The modulus operator with the  $2\pi$  argument gives the needed on sequence that will be sent to the gate opto-coupler block, which will feed each sixpulse converter. The off sequence turns out on a similar way but waiting 180° to keep the same on and off duration in each IGBT.

# 4.3. Seven-Level Pulse Generator

To operate the seven-level inverter, six times the frequency of the six-pulse generator must be ensured. This is achieved by monitoring the falling border in the novel PLL output signal, using it along with the modulus operator with the  $\pi/3$  argument. This signal will be the period for the seven-level generator which will change its state each  $\pi/42$  rad.

# **5. VSC ASSEMBLING**

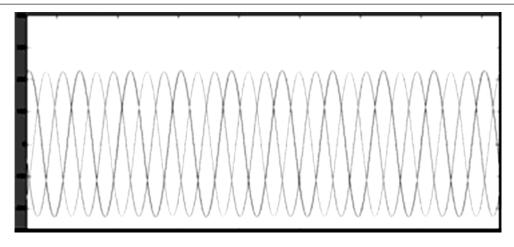

The 84-pulse VSC along with the PLL to synchronize it to the grid has been assembled in a low power lab prototype. The following figures exhibit some results. Fig. 7 illustrates the 84pulse output, while Fig. 8 depicts its corresponding harmonic content. It is important to observe that the scale provided by oscilloscope is on decibels and is very close to Fig. 4. Fundamental frequency is 60 Hz and the main harmonics are about each 5 kHz,

# 6. SIMULATION RESULTS

The test system results are the following :

Fig. 6. Source current waveforms before applying 84-pulse STATCOM.

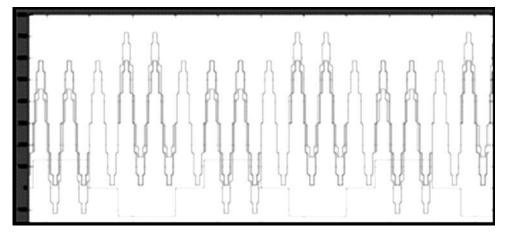

Fig. 7. Test system control strategy generated 84- pulse wave form.

Fig. 8. DC voltage waveform of the 84-pulse STATCOM.

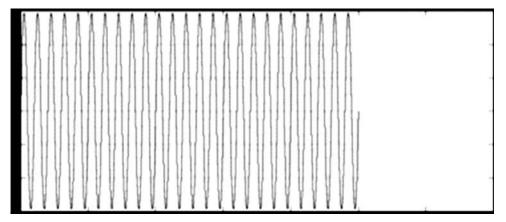

Fig. 9. Source current waveforms after applying 84-pulse STATCOM.

## **5. CONCLUSION**

This paper proposes about xplains about the performance of statcom based on 84 pulse voltage source converter configuration using multilevel converters reinjection concept which is to attain an 84 pulse vsc with the low THD, which will be assumed by the combination of one-twelve pluse converter and a seven-level converter. The design performance will allows to verify the harmonic content of the resultant voltgae signal. The assumed low THD, allows the system to be used in the basement of FACTS devices or as in the especial applications. The three-phase PLL is used to synchronoize the firing signals in all switches. Because of the H-brigde multilevel concept the size of the construction is reduced with out adding more number of switches.

#### **6. REFERENCES**

- Hingorani, N. G.: "FACTS Technology State of the Art, Current Challenges and the Future Prospects," IEEE Power Engineering Society General Meeting, 24-28 June 2007, Tampa, Florida USA

- 2. Song, Y. H., and Johns, A. T.: 'Flexible AC transmission systems FACTS,' (IEEE Power and Energy Series 30, 1999)

- Acha, E., Fuerte-Esquivel, C. R., Ambriz, H., Angeles, C.: 'FACTS. Modelling and Simulation in Power Networks.' (John Wiley and Sons, LTD, 2004.)

- Wang, H. F.: "Applications of damping torque analysis to StatCom control", Electrical Power and Energy Systems, Vol. 22, 2000, pp. 197-204.

- 5. CIGRE, "Static Synchronous Compensator", CIGRE working group14.19, September 1998.

- 6. Hingorani, N. G., and Gyugyi, L.: 'Understanding FACTS,' (IEEE Press 2000).

- El-Moursi, M. S., and Sharaf, A. M.: "Novel Controllers for the 48-Pulse VSC Stat Com and SSSC for Voltage Regulation and Reactive Power Compensation",

- 8. IEEE Transactions on Power Systems, Vol. 20, No. 4, November 2005, pp. 1985-1997

- 9. Pan, W., Xu, Z., Zhang, J.: "Novel configuration of 60-pulse voltage source converter for StatCom application," International Journal of Emerging Electric Power Systems, Vol 8, Issue 5, 2007, Article 7.

- Liu, Y. H., Arrillaga, J., Watson, N. R.: "A New STATCOM Configuration Using Multi-Level DC Voltage Reinjection for High Power Application", IEEE Transactions on Power Delivery, Vol. 19, No. 4, October 2004, pp. 1828-1834.

- Arrillaga, J., Liu, Y. H., Watson, N. R.: 'Flexible Power Transmission, The HVDC Options.' (John Wiley & Sons, Ltd, 2007, pp. 169-223.)

- Liu, Y. H., Watson, N. R., Arrillaga, J.: "A New Concept for the Control of the Harmonic Content of Voltage Source Converters", The Fifth International Conference on Power Electronics and Drive Systems, 2003, 17-20 Nov. 2003, pp. 793-798 Vol.1

- Rodriguez, J., Sheng, L. J., Peng, F. Z.: "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Transactions on Industrial Electronics, Volume 49, Issue 4, Aug. 2002 pp. 724 –738.

- Krause, P. C., Wasynczuk, O., and Sud, S. D.: 'Analysis of Electric Machinery an Drive Systems, Second Edition,' (IEEE Series on Power Engineering, pp. 487,2002)

- Liu, Y. H., Perera, L. B., Arrillaga, J., and Watson, N. R.: "Harmonic Reduction in the Double Bridge Parallel Converter by Multi-Level DCVoltage Reinjection," 2004 International Conference on Power System Technology POW-ERCON 2004, 21-24 November 2004

- Han, B., Choo, W., Choi, J., Park, Y., Cho, Y.: "New Configuration of 36-Pulse Voltage source Converter Using Pulse-Interleaving Circuit", Proceedings of the Eight International Conference on Electrical Machines and Systems 2005, September 27-29, 2005

- 17. IEEE Std 519-1992: IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, 1992.

- Aredes, M., Santos Jr., G.: "A Robust Control for Multipulse StatComs," Proceedings of IPEC 2000, Vol. 4, pp. 2163 - 2168, Tokyo, 2000.

- Cho, J. H., Song, E. H.: "Stationary Reference Frame-Based Simple Active Power Filter with Voltage Regulation", Industrial Electronics, 2001. Proceedings. ISIE 2001. IEEE International Symposium on, Vol. 3, June 2001, pp. 2044-2048

- Mussa, S. A., Mohr, H. B.: "Three-phase Digital PLL for Synchronizing on Three- Phase/Switch/Level Boost Rectifier by DSP", 35th Annual IEEE Power Electronics Specialists Conference Aachen, Germany, 2004, pp. 3659-3664

- Voraphonpiput, N., Chatratana, S.: "Analysis of Quasi 24-Pulse Stat Com Operation and Control Using ATP-EMTP," TENCON 2004. 2004 IEEE Region 10 Conference, Nov. 2004 Vol. 3, pp. 359-362