# A Novel on Single Phase Asymmetrical Multilevel Inverter with Reduced Number of Switches

# K. Vinoth\*, K.Nanda Kumar\* and S. Aravinth Raj\*

#### ABSTRACT

Solar energy is most energizing energy used in industrial level. This paper proposes an Asymmetrical Fifteen level cascaded H-Bridge circuit topology. The input DC voltages from PV solar panels are fed to the DC-DC boost converter to obtain maximum power by using maximum power point tracking method (MPPT). The output from the converter is given to this H-Bridge circuit which gives AC voltage. The output voltage will be step by step increase waveform with multiple levels. The output power can be i m p r o v e d using LCL filter circuit and the output is fed to AC load. Simulation and analysis result can be achieved by this topology.

**Keywords:** Dc-Dc Step up converter, FPGA integrated circuit, Cascaded H-Bridge inverter with Bi-directional switches IGBT, Total harmonic distortion (THD).

## 1. INTRODUCTION

Renewable energy technologies are pure green sources of energy that have much less environmental impact than any other conventional energy generation technologies. Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel inverter system for a high power application. Capacitors, batteries and renewable energy voltage sources can be used as the multiple dc voltage sources. It holds high potential to meet our energy demands. These renewable energy sources can be easily used to run turbines in a generative process thus it replace oil, minerals and natural gas. As for wind and solar energy, these technologies related to reaping energy out of these is still in development. This inverter topology has higher efficiency and controlling various several power terminals with low cost. This paper mainly focused on the development of a solar PV system with high efficiency multilevel inverter controlled by FPGA (Field Programmable Gate Array). The DC power output from the solar panel is converted to AC power by using an asymmetrical multi-level cascaded H- bridge inverter configuration which gives quality power to the load.

# 2. MULTILEVEL INVERTER

This proposed multilevel inverter produces an output waveform that shows multiple steps at several voltage levels. A multilevel inverter not only achieves high power ratings, but also enables the use of renewable energy sources. Multilevel inverter has high potential to give a highly improved output power by generating multiple steps in output voltage. However, the other two types of multilevel inverter increases in number of switching devices other components increases, which leads to complexity of circuit and more switching losses, whereas in this proposed system the switches are reduced to seven switches in order to reduces switching losses. Many multilevel inverter circuits have been researched for high efficiency output wave, whereas the Cascaded multilevel control method is very easy when compare to other multilevel inverter

KCG College of Technology, Chennai, India, E-mail: vinothkrishna03, nandakumar9550, saravinth987@gmail.com

because it doesn't require any clamping diode and flying capacitor to reduce the losses. Multilevel inverters have potential to overcome a conventional two level converter that has high switching frequency pulse width modulation. The features of asymmetrical multilevel inverter can be summarized in brief as staircase waveform which produces the output power with low level distortion and also it reduces the dv/dt stresses, therefore no electromagnetic interference to the equipment can be totally eliminated. Multilevel inverters produces very low level Common Mode voltage, therefore the stress on the cables of a motor is connected to the motor drives can be reduced in multilevel inverter. Further Common Mode voltages can be rejected by using advanced modulation techniques. Multilevel inverters can draw high rated input current with less harmonic distortion. This proposed system can be operated at both fundamental frequency and high switching frequency with less electromagnetic interference with the help of pulse width modulation techniques. If there is a low switching frequency means it makes the inverter to operate in lower switching losses and produces higher efficiency power. There are several multilevel converters and inverters are commercialized for high power applications such as Automotive applications, Variable speed motor drives, Active filters etc.

## 3. PROPOSED SYSTEM OF MULTILEVEL INVERTER

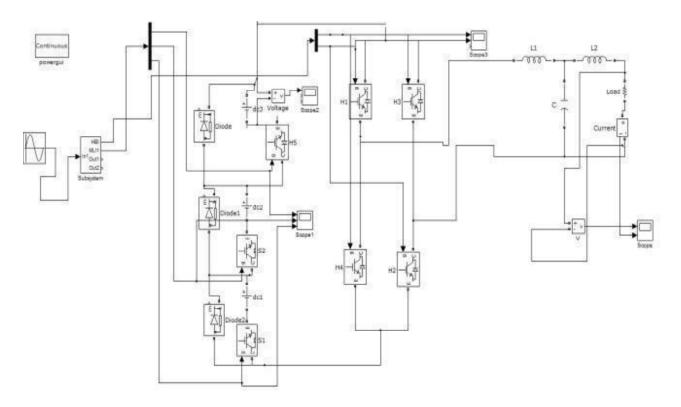

The proposed Asymmetrical Multilevel inverter circuit was developed from the nine level inverter circuits. It consists of single-phase conventional H-bridge inverter, two capacitor voltage divider as shown in Fig. And bidirectional switches used is Insulated Gate Bipolar Transistor (IGBT). The modified cascaded H-bridge topology has lower power switches, power diodes, and less number of capacitors for inverters of the same number of levels. A number of photovoltaic panels were formed as arrays were connected to the asymmetrical multilevel inverter through DC–DC boost converter. DC bus voltages are necessarily high to ensure that power flows from the PV arrays to the load. The switching pattern of the inverter can produce fifteen levels output-voltages (7/7Vdc,6/7Vdc,5/7Vdc,4/7Vdc,3/7Vdc,2/7Vdc,1/7Vdc, 0) and same its negative voltage level of the DC supply voltage.

Figure 1: Asymmetrical Fifteen level Inverter Simulation diagram

| Voltage              | S <sub>3</sub> | S2        | <b>S</b> <sub>1</sub> | H <sub>1</sub> | H <sub>2</sub> | H <sub>3</sub> | $\mathbf{H}_4$ |

|----------------------|----------------|-----------|-----------------------|----------------|----------------|----------------|----------------|

| Level                |                |           |                       | ÷              |                |                |                |

| V <sub>de</sub>      | ON             | ON        | ON                    | ON             | ON             | OFF            | OFF            |

| 6/7V <sub>dc</sub>   | ON<br>ON       | ON<br>OFF | OFF<br>ON             | ON<br>ON       | ON<br>ON       | OFF<br>OFF     | OFF<br>OFF     |

| 5/7 V <sub>dc</sub>  |                |           |                       |                |                |                |                |

| $4/7  V_{dc}$        | ON             | OFF       | OFF                   | ON             | ON             | OFF            | OFF            |

| 3/7 V <sub>dc</sub>  | OFF            | ON        | ON                    | ON             | ON             | OFF            | OFF            |

| 2/7 V <sub>dc</sub>  | OFF            | ON        | OFF                   | ON             | ON             | OFF            | OFF            |

| $1/7  V_{dc}$        | OFF            | OFF       | ON                    | ON             | ON             | OFF            | OFF            |

| 0                    | OFF            | OFF       | OFF                   | OFF            | OFF            | OFF            | OFF            |

| -1/7 V <sub>dc</sub> | OFF            | OFF       | ON                    | OFF            | OFF            | ON             | ON             |

| -2/7 V <sub>dc</sub> | OFF            | ON        | OFF                   | OFF            | OFF            | ON             | ON             |

| -3/7 V <sub>dc</sub> | OFF            | ON        | ON                    | OFF            | OFF            | ON             | ON             |

| -4/7 V <sub>dc</sub> | ON             | OFF       | OFF                   | OFF            | OFF            | ON             | ON             |

| -5/7 V <sub>dc</sub> | ON             | OFF       | ON                    | OFF            | OFF            | ON             | ON             |

| -6/7V <sub>dc</sub>  | ON             | ON        | OFF                   | OFF            | OFF            | ON             | ON             |

| -V <sub>dc</sub>     | ON             | ON        | ON                    | OFF            | OFF            | ON             | ON             |

Figure 2: Switching States of multilevel inverter

# 4. PWM PULSE GENERATION

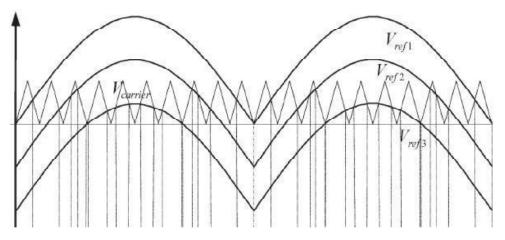

The pulse width modulation (pwm) signal was generated in this inverter a single reference sine wave with a frequency of 50HZ is compared with triangular carrier wave with frequency of 10kHZ. The amplitude of the sine wave is taken in different offset values. The three offset sine wave was compared with a triangle wave and the pulse width modulation.

Figure 3: PWM Generation Technique

# 5. DISCUSSIONS ON SIMULATION RESULT

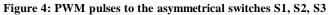

Matlab Simulink is used to simulate the proposed multilevel inverter circuit and it was done as a prototype. The different amplitude of reference signal sine reference wave is compared with a multi carrier triangle wave to generate the sine PWM signal. Here the switching device is seven bidirectional switches are IGBT as shown in diagram Fig.1. The processor used here is XILINS SPARTAN 6E (Field Programmable Gate Array). It's used under the category of Very large scale integration system. In XILINS SPARTAN 6E FPGA many of the pins can be used as either input or output pins. The operating speed of the Spartan 6E controller is much greater than other DSP chips. These controllers act as a function generator which is used to generate signals. Here it is used to generate multicarrier sine PWM pulses to the switches.

Figure 5: Matlab simulation Pulse Generation for S1, S2, S3

Figure 6: Matlab Simulink PWM pulses to the Inverter switches S4.S5.S6,S7

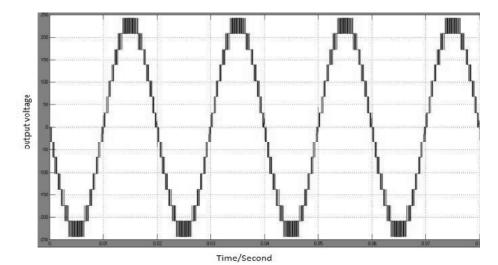

The figure shows the fifteen level inverter output voltage by using Mat lab simulation

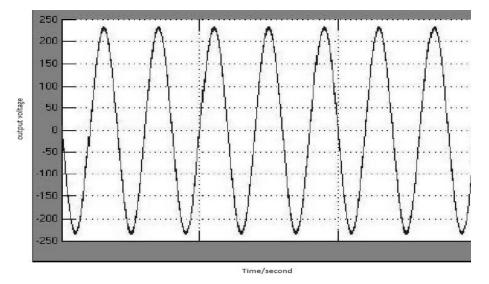

Figure 8: Fifteen level inverter output voltage with Filter

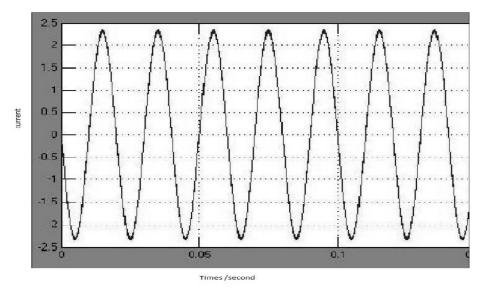

Figure 9: Fifteen level Inverter output current

# 6. HARDWARE RESULT

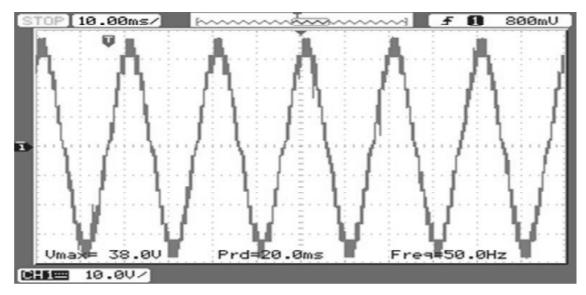

Figure 10: Fifteen level inverter hardware output voltage

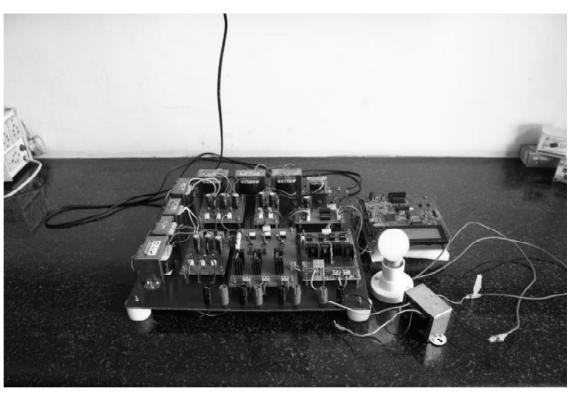

Figure 11: Experimental setup for the single phase fifteen levels PWM inverter.

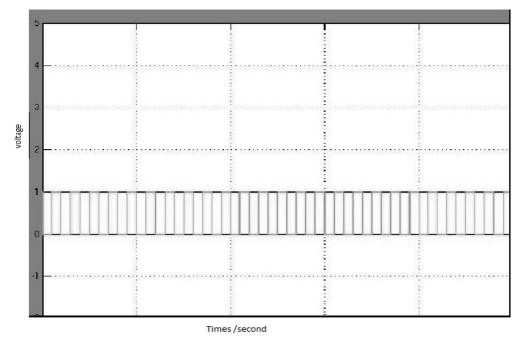

# 6. THD ANALYSIS

The total harmonics distortion result is analyzed by using YOKOGAWA.

# 7. CONCLUSION

This inverter output was improved by its output voltage waveforms and low harmonics level. This paper has proposes a novel on multicarrier Pulse width modulation, switching topology for the proposed asymmetrical multilevel inverter circuit. In this paper single sine reference signal is compared with a multi

|                                        |         |     | Order  | U3 [V] | hdf[%] | Order | 13 [A] | hdf[%] | CF:3                   |

|----------------------------------------|---------|-----|--------|--------|--------|-------|--------|--------|------------------------|

|                                        |         |     | Total  | 12.857 |        | Total | 0.0000 |        | Element 1 HR           |

| fPLL1:U3                               | 53.309  | Hz  | ] dc[  |        |        | dc    |        |        | 11 2A                  |

| fPLL2:11                               | Error   |     | 1      | 12.823 | 99.733 | 1     | 0.0000 | 15.209 | Sync Src:[1]           |

| 00000000000000000000000000000000000000 |         |     | 2      | 0.027  | 0.207  | 2     | 0.0000 | 18.328 | Element 2 HR           |

| Urms3                                  | 12.850  | ٧   | 3      | 0.065  | 0.509  | 3     | 0.0000 | 1.832  | 12 28                  |

| lrms3                                  | 0.0000  | A   | 4 [    | 0.031  | 0.240  | 4     | 0.0000 | 22.359 | Sync Src:12            |

| P3                                     | -0.000  | Ħ   | 5 [    | 0.255  | 1.986  | 5     | 0.0000 | 0.915  | Element 3 IHR          |

| S3                                     | 0.000   | VA  | 6[     | 0.115  | 0.897  | 6     | 0.0000 | 4.694  | U3 10V                 |

| Q3                                     | 0.000   | var | 7      | 0.106  | 0.826  | 7     | 0.0000 | 17.251 | 13 2A<br>Sync Src:[13] |

| λ3                                     | Error   |     | 8      | 0.059  | 0.461  | 8     | 0.0000 | 14.168 | Element 4 IHR          |

| <b>\$</b> 3                            | Error   |     | ] 9[   | 0.062  | 0.481  | 9 [   | 0.0000 | 17.862 |                        |

| -                                      |         |     | 10     | 0.037  | 0.291  | 10    | 0.0000 | 6.139  | 14 <u>5</u> A          |

| Uthd3                                  | 7.307   | %   | ] 11 [ | 0.537  | 4.173  | 11    | 0.0000 | 4.784  | Sync Src:14            |

| 1thd3                                  | 98.837  | %   | 12     | 0.069  | 0.541  | 12    | 0.0000 | 17.803 | Element 5 MR           |

| Pthd3                                  | 0.437   | %   | 13     | 0.379  | 2.944  | 13    | 0.0000 | 15.287 | U5 600V<br>15 5A       |

| Uthf3                                  | 7.438   | %   | 14     | 0.055  | 0.428  | 14    | 0.0000 | 7.976  | Sync Src:15            |

| lthf3                                  | 132.614 | %   | ] 15 [ | 0.195  | 1.520  | 15 [  | 0.0000 | 5.638  | Element 6 MR           |

| Utif3 -                                | 0 F     |     | 16     | 0.040  | 0.309  | 16    | 0.0000 | 18.642 | U6 600V                |

| Itif3 -                                | 0 F     |     | 17     | 0.293  | 2.277  | 17    | 0.0000 | 10.828 | 16 5A<br>Sync Src:16   |

| hvf3                                   | 2.092   | %   | 18     | 0.037  | 0.286  | 18    | 0.0000 | 8.596  |                        |

| hcf3                                   | 25.954  | %   | 19     | 0.020  | 0.156  | 19    | 0.0000 | 17.666 |                        |

| Kfact3                                 | 2.3713  | k   | 20     | 0.026  | 0.204  | 20    | 0.0000 | 22.924 |                        |

Figure 12: THD Hardware Result

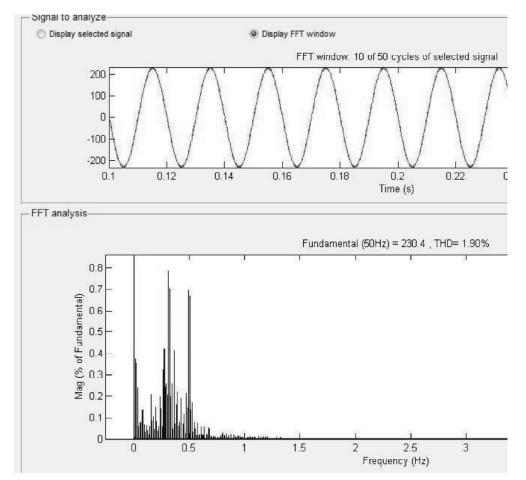

Figure 13: Total Harmonic Distortion & FFT Analysis

triangular wave signal to generate the PWM signals. Here there are three different DC voltage levels are used for the two H-Bridge inverters. So this proposed method of configuration is known as asymmetrical cascaded H bridge inverter and by driving the modulation index variously and different levels of DC voltages the fifteen levels of the output voltages produced. An FPGA XILINS SPARTAN 6E is optimized and the performance of the inverter is achieved. The achieved THD level of this fifteen level inverter is 1.90 %. We can give the fifteen level output voltage of matrix converter from that can we get a variable AC output voltage. This asymmetrical f i f teen level inverter is applicable for all industrial AC Loads. The output of fifteen level can be increased to seventeen level and further more. Renewable energy source when used in an effective manner the overall system efficiency can be increased.

### REFERENCES

- [1] L G. Franquelo, J. Rodríguez, J. I. Leon, S. Kouro, R. Othello, and M. A.M. Prats, <sup>-</sup> The age of multilevel converters arrives, *IEEE IND. Electron. Magazine*, June 2008.

- [2] A.Jidin,N.R, N.R, N.R. N. Idris, A. H. M. Yatim, t. Sutikno and E. Elbuluk, An optimized switching strategy for quick dynamic torque control in DTC-hysteresis-based induction machines," *IEEE trans. IND. Electron.* Vol. 58, no. 8, pp 33913400, Aug.2011.

- [3] E. Najafi and H. M. Yatim, Design and Implementation of a new multilevel inverter topology, IEEE IND. Electron., Vol. 59, no. 11, Nov 2012.

- [4] M. F. Kangarlu, E. Babaei, A generalized cascaded multilevel inverter using a series connection of sub multilevel inverters, *IEEE Trans. Power Electron*, Vol. 28, no. 2, pp. 625-636, Feb 2013.

- [5] P. K. Hinga, T. Ohnishi, and T. Suzuki, A new PWM inverter for photovoltaic power generation system, in *Conf. Rec. IEEE Power Electron. Spec. Conf.*, 1994, pp. 391–395.

- [6] E. Babaei, A new cascaded multilevel inverter topology with minimum switches, *IEEE Trans. Power Electron*. Vol 23, no. 6, pp. 2657-2664, Nov.2008

- [7] S.B. Kjaer, J. K. Pedersen, and F. Blaabjerg, A review of single-phase grid connected inverters for photovoltaic modules, *IEEE Trans. IND Appl.*, vol. 41, no. 5, pp. 1292–1306, Sep. /Oct. 2005.

- [8] Li S, Rodriguez J, Peng GS (2002) Multilevel inverters: a survey of topologies, controls and applications. IEEE Trans IND Electron 49:724–738.

- [9] Daher S, Schmid J, Antunes FLM (2008) Multilevel inverter topologies for stand-alone PV systems. IEEE Trans IND Electron 55:2703–2712.

- [10] Bhagwat PM, Stefanovic VR (1983) Generalized structure of a multilevel PWM inverter. IEEE Trans IND Appl 1A– 19:1057–1069.

- [11] M. Calais and V. G. Agelidis, "Multilevel converters for single-phase grid connected photovoltaic systems—An overview, in *Proc. IEEE Int. Symp IND. Electron.*, 1998, vol. 1, pp. 224–229.