# Comparative Study of PLL Based Grid Synchronization Algorithms for Single Phase System

\*Radhika Urhekar \*\*Prof. Mrs. S.U.Kulkarni

*Abstract :* PLL is a technique in control system which is largely used in synchronization schemes in various fields, commonly in communication field and Power Electronics. Taking into consideration its importance, PLL is being a matter of significant interest and different techniques along with improvements has been put forward for its execution. PLL is used for synchronization between power converter and the grid. Here an attempt has been made to emphasize on and differentiate the performance for three existing PLL schemes for single phase system. They are Basic PLL, Quadrature signal generator (QSG) and Parks transform based PLL and Second Order Generalized Integrator (SOGI) based PLL. The design of Phase Detector block of Basic PLL is further modified in other two schemes mentioned above. These schemes are proposed with an aim to detect grid parameters accurately so as to facilitate grid synchronization between power converter and grid.

*Keywords* : Basic PLL, Quadrature signal generator and Parks transform based PLL, SOGI PLL, grid connected inverter

## **1. INTRODUCTION**

Synchronization of electronic oscillator automatically was first suggested in 1923 by Appleton. In 1932 H. De Bellescise proposed the idea of Phase Lock Loop (PLL). Phase Lock Loop was widely used after the emergence of Signetics monolithic IC dependant systems. PLLs are extensively used in various industrial fields such as communication systems, motor control systems, induction heating power supplies and contactless power supplies Currently PLL schemes are used in grid-connected converters. It is essential for effective transmission of power to grid that the inverter is in synchronism with the utility grid. Phase Locked Loop is an algorithm which is largely used for synchronization in the inverters.

## 2. BASIC THEORY OF PLL

The operation of devices like PV connected inverters which feeds power to the grid requires information about phase angle of the grid. Phase Locked Loop system is based on close loop where feedback is used to control internal oscillator which keeps phase, time of external signal.PLL is basically a servo system which aims at controlling the phase of signal at its output so as to minimize the phase error that occurs between phase of reference and the output. Performance of control loop in grid connected systems depends upon quality of lock. In conditions like notching, voltage unbalance, variation in frequency, phase angle jump, harmonic disturbances, PLL must be capable to reject the sources which causes errors and should be able to maintain perfect lock condition with grid voltage.

<sup>\*</sup> Department of Electrical Engineering Bharati Vidyapeeth Deemed University College of Engineering, Pune, Maharashtra, India radhikaurhekar@gmail.com,

<sup>\*\*</sup> Department of Electrical Engineering Bharati Vidyapeeth Deemed University College of Engineering, Pune, Maharashtra, India sukulkarni@bvucoep.com

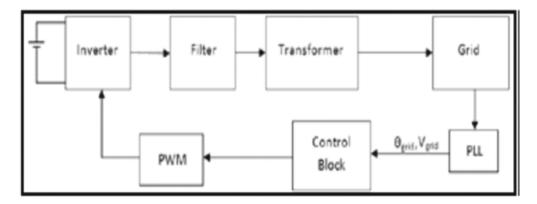

Fig.1. Synchronization method based on PLL for inverter connected to grid

### **3. PLL TECHNIQUES**

#### A. Basic PLL

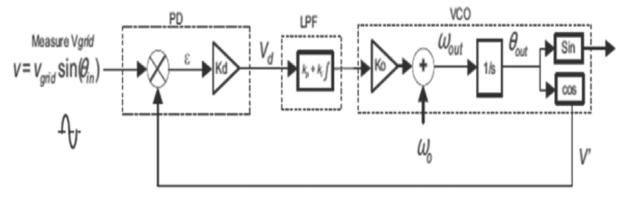

Fig. 2. Basic Structure of PLL

The measured grid voltage can be given as follows

$$V = V_{\text{grid}} \sin(\theta_{\text{in}}) = V_{\text{grid}} \sin(\text{Wgrid} t + \theta_{\text{grid}})$$

(1)

Assuming that VCO generates sine wave near to grid, the VCO output can be stated as

$$V' = \cos(\theta_{out}) = \cos(W_{PLL} t + \theta_{PLL})$$

(2)

Comparison of input sine with locked sine obtained from VCO generates error signal which is in proportion to angle error. Phase Detector block multiplies these two quantities to get

$$Vd = \frac{KdV_{grid}}{2} [sin ((W_{grid} - W_{PLL})t + (\theta_{grid} - \theta_{PLL}) + sin ((W_{grid} + W_{PLL})t + (\theta_{grid} - \theta_{PLL})] (3)$$

PD block shows locking error, but it is not linear in nature and contains component which changes at double the grid frequency. This higher frequency component should be removed.

Ignoring double frequency component, lock error is as follows

$$Vd' = \frac{KdV_{grid}}{2}\sin\left((W_{grid} - W_{PLL})t + (\theta_{grid} - \theta_{PLL})\right)$$

(4)

For steady state operation,  $W_{grid} - W_{PLL}$  the term can be ignored, for small values of theta *sin* ( $\theta$ ) ~  $\theta$ . Hence, linearized error is given Comparative Study of PLL Based Grid Synchronization Algorithms for Single Phase System

$$e_{rr} = \frac{V_{\text{grid}}(\theta_{\text{grid}}(\theta_{\text{grid}} - \theta_{\text{PLL}}))}{2}$$

(5)

This error is the input to loop filter, which is nothing but a PI controller, which is used to reduce the locking error to zero at steady. The disadvantage of this PLL is that the roll off given by PI controller is not as per desired value and presents high frequency component in output of loop filter. This affects the ability of PLL.

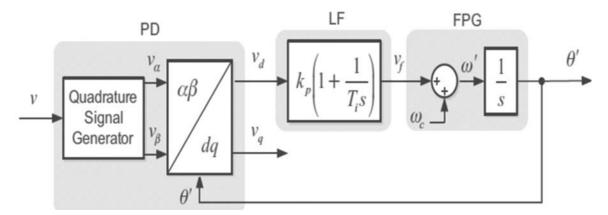

#### B. Quadrature Signal Generator (QSG) and Parks Transform based PLL

The difference between the basic PLL mentioned above and the QSG-PLL is the Phase Detector block. Quadrature signal generator and Parks Transformation together constitute the Phase Detector block. Quadrature signal generator acts as Clarks Transformation which produces two signals which have phase difference of 90 degree between them. These quadrature signals are then given to Parks Transformation block which converts stationary reference frame signals to rotating frame of reference signals. It generates two components such as direct axis (d) and quadrature axis (q) which are given as input to PI controller

$$V_{\alpha} = V_{in} \sin \theta \tag{6}$$

The Park transformation output can be denoted as

$$V_{\beta} = V_{\text{in}} \sin\left(\theta - \frac{\pi}{2}\right) \tag{7}$$

$$V_{d} = V_{\alpha} \sin(\theta') + V_{\beta} \cos(\theta')$$

(8)

$$V_q = -V_{\alpha} \cos(\theta') + V_{\beta} \cos(\theta')$$

(9)

Substituting (6),(7),(8),(9) we get

$$V_d = V_{in} \sin(\theta) \sin(\theta') - V_{in} \sin\left(\theta - \frac{\pi}{2}\right) \cos(\theta')$$

(10)

$$V_q = -V_{\text{in}}\sin(\theta)\cos(\theta') - V_{\text{in}}\sin\left(\theta - \frac{\pi}{2}\right)\sin(\theta')$$

(11)

Equation (9) can be rewritten as

$$V_q = -V_{in}\sin(\theta)\cos(\theta') - V_{in}\cos(\theta)\sin(\theta')$$

(12)

When calculated for  $\nabla q = 0$ , we obtain  $\theta = \theta' + 2n\pi$  which practically can be written as  $\theta = \theta'$ . Hence phase angle detected by PLL is equal to phase angle of grid.

Fig. 3. Quadrature signal generator and Park Transform based PLL.

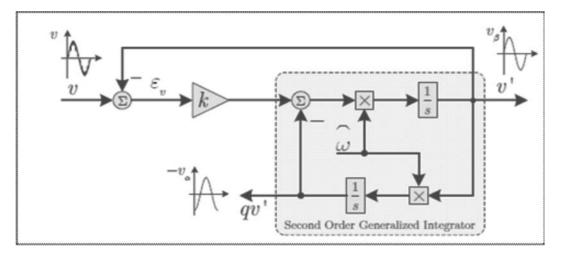

#### C. Second Order Generalized Integrator (SOGI) based PLL

SOGI based PLL varies from Quadrature signal generator and Parks Transformation based PLL in the way in which quadrature signal are produced. As output signals, two sine waves V' and qV', with a phase shift of  $\pi/2$  are generated.

4471

The component V' has the same phase and amplitude as the

Fundamental of the input voltage signal (v).

The closed loop transfer functions  $H_d(V'/v)$  and  $H_q(qV'/v)$  are defined as follows

$$H_{q}(s) = \frac{V'}{V}(s) = \frac{k ns}{s^{2} + k ns + n^{2}}$$

$$Hq(s) = \frac{qv}{V}(s) = \frac{k hs}{s^2 + k hs + h^2}$$

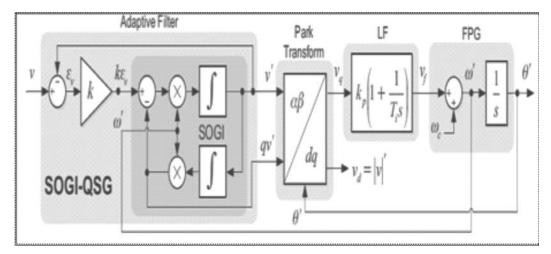

Fig. 4. SOGI based Orthogonal Signal Generator.

Where  $\omega n$  is the angular frequency of the signal and *k* is a constant that determines the bandwidth of the filters.

As can be seen, the transfer function for  $H_d$  resembles that of a Band Pass Filter, that filters out harmonic and random noise and whose output is in phase with that of the input signal. The transfer function for  $H_q$  is the same as that of a second order Low Pass Filter, that not only filters out harmonics and random noise, but also introduces a phase shift of  $\pi/2$  radians.

Fig. 5. Structure of SOGI-PLL.

The performance of the SOGI orthogonal signal generator depends on the term ùn which is the angular frequency of the signal. Thus, it is calculated and adjusted in the SOGI by the PLL so as to make it frequency adaptive

# 4. SIMULATION

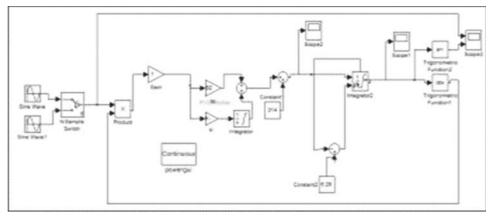

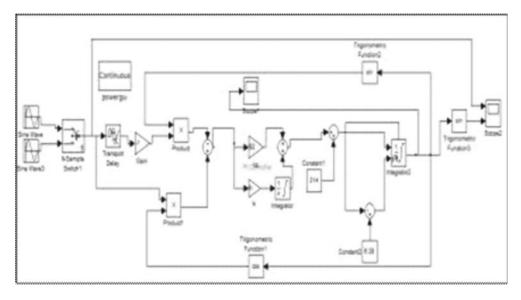

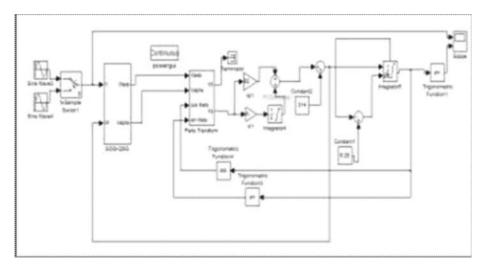

Fig. 6. (b)

PLL above are simulated in MATLAB/Simulink .The simulation models are as shown (a) Basic PLL (b) Quadrature signal generator and Park Transform based PLL (c) SOGI PLL

# 5. EXPERIMENTATION AND RESULT

The performance of the PLL is studied under Power Quality variations such as Frequency variation, Phase angle jump, Harmonic Distortion. The duration in which PLL synchronizes with the grid conditions determines the suitability and performance of PLL.

# A. Frequency Variation

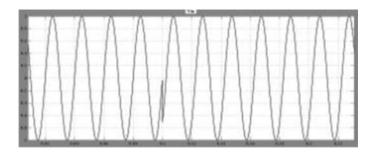

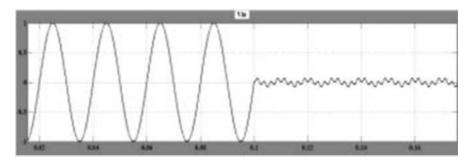

Fig.7. (a) Input voltage with Frequency variation.

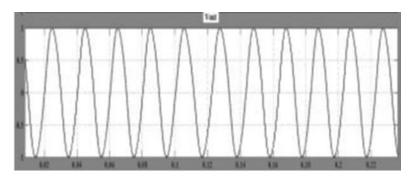

Fig.7. (*b*)

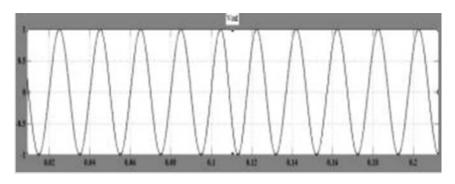

**Fig.7.** (*c*)

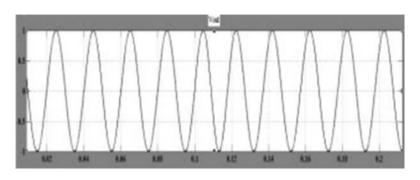

Fig.7. (*d*)

Fig.7 (a) Grid voltage under Frequency variation which is given as input to PLL (b) Output voltage of Basic PLL (c) Output voltage of QSG-PLL (d) Output voltage of SOGI PLL

Frequency variation occurs at 0.1 seconds .It is seen that Basic PLL synchronizes with the change in frequency at 0.2 seconds. Quadrature signal generator and Park transform based PLL and SOGI matches the grid conditions at 0.18 seconds. QSG-PLL and SOGI –PLL are faster than Basic PLL in capturing grid conditions.

### **B.** Phase angle jump

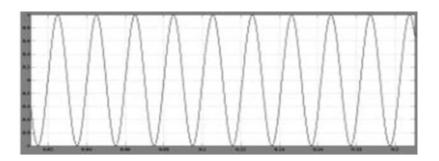

Fig. 8. (a) Input voltage with Phase angle Jump.

#### Fig. 8. (b)

Fig. 8. (c)

Fig. 8. (*d*)

Fig.8 (a) Voltage at grid during Phase angle jump (b) Response of Basic PLL (c) Response of QSG-PLL (d) Response of SOGI PLL

Phase angle jump from 0 to 45 degrees occurs at 0.1 seconds. Basic PLL synchronizes with change in phase angle at 0.2 seconds. QSG-PLL and SOGI–PLL synchronizes at 0.18 seconds. Here we conclude that approximately PLL takes 0.1 seconds to synchronize with the grid.

### C. Harmonic Distortion

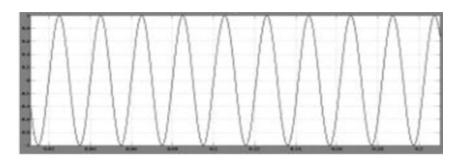

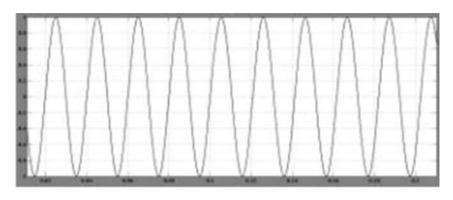

Fig. 9. (a) Input voltage during Harmonic Distortion.

Fig. 9. (b)

Fig. 9 (a) shows grid voltage during Harmonic Distortion (b) Response of Basic PLL (c) Response of QSG-PLL (d) Response of SOGI-PLL

Output voltage of PLL shows that it rejects harmonics and responds to only fundamental component of grid frequency. Here PI controller rejects the higher frequency components. It can be concluded that PLL can work efficiently in harmonic condition. This makes performance of PLL reliable for grid synchronization.

## 6. CONCLUSION

The performances of the three algorithms used for single phase system are studied under Power Quality variations. The results show that the synchronization time required for the PLL to lock the grid conditions is 0.1 seconds. QSG-PLL and SOGI-PLL are best suited for single phase applications. It shows that the operation of system is spontaneous even under disturbance. PLL gives information about phase and frequency of the grid which is useful to design the control strategy of inverter such that proper synchronization is maintained between PV system and the grid.

## 7. REFERENCES

- 1. Texas Instruments Application Report SPRABT3 July- 2013

- 2. Comparative study of single phase PLL algorithm for grid synchronization application-IJECT Vol. 3, Issue 4, Oct Dec 2012

- 3. Guan-Chyun Hsieh, James C. Hung,"Phase Locked Loop Techniques-A Survey", in IEEE Transactions on Industrial Electronics, Vol. 43, No. 6, December 1996.

- Pota, H. R,"Phase Locked Loop", University of New SouthWales (UNSW), Australia, (Technical Brief Lecture Notes) (2005).

- A. Timbus, M. Liserre, R. Teodorescu, F. Blaabjerg, "Synchronization Methods for Three Phase Distributed Power Generation Systems. An Overview and Evaluation", in Power Electronics Specialists Conference, 2005. PESC '05. IEEE 36th, 2005, pp. 2474-2481.

- 6. Mihai Ciobotaru, Remus Teodorescu, Frede Blaajberg, "Improved PLL structures for single phase grid inverters", in Proceedings of PELINCEC'05.

- 7. Mihai Ciobotaru, Remus Teodorescu, Frede Blaajberg, "A New Single-Phase PLL Structure Based on Second Order Generalised Integrator", in Power Electronics Specialists Conference, 2006. PESC '06. 37th IEEE, 2006.