# International Journal of Control Theory and Applications

ISSN: 0974-5572

© International Science Press

Volume 10 • Number 12 • 2017

# **Network-On-Chip by using Power Reduction Technique**

# A. Manikandan<sup>a</sup> and P. Nirmal Kumar<sup>b</sup>

<sup>a</sup>Assistant Professor, Department of Electronics and Communication Engineering, M. Kumarasamy College of Engineering, Karur, Tamil Nadu, India

<sup>b</sup>Assistant Professor, Department of Electronics and Communication Engineering, Arulmurugan College of Engineering, Karur, Tamil Nadu, India

*Abstract:* Lately, the nature of interconnection framework turns out to be more huge since the quantity of centers incorporated into System on chip increments. As the innovation recoils, the power dispersal of the connections battles with the power disseminated in different components. The system interface encodes the flutters before they are infused into the system. In this paper a Novel Data Encoding Schemes are utilized with Pre-calculation rationale to decrease exchanging action that lessens the power scattering by the system joins. The Power dissemination can be adequately lessened in this Data Encoding Technique.

Keywords: Switching activity, power analysis, Data Encoding, network links, NOC.

### **1. INTRODUCTION**

In current processors, the aggregate power scattered in the interconnects is expanded and it is relied upon to increment in future. So the power scattered by the system connections can be lessened. In this paper we concentrate on the systems to diminish the power scattered by the connections. The connection control dispersal is as identified with the switch and system interface control scattering. This power dispersal may increment as for the innovation change. We show a Data encoding plans that lessens the exchanging action and coupling exchanging movement for each piece on connections of the directing way. The proposed strategy is utilized to decrease power is checked in reproduction in both algorithmic and building level. In future the on chip correspondence issue has turned out to be more huge contrasted with other calculation issues. In correspondence subsystem territory, vitality utilization, control dispersal, also, cost has progressively gets influenced. The significance of interconnects in complex many-centers chips has beaten the significance of transistors as a prevailing variable of execution, power, cost and unwavering quality [1]-[2]. The connection power is viewed as more huge contrasted with the transistor control. The execution, power can be acquired with design of Network-on-chip that delineates the future encompassing keen applications.

#### 2. RELATED WORKS

Since the innovation recoils, the transistor has been decreased in range and power. In future, it prompts to the interconnection joins. So the writing about the interconnection is talked about. There are numerous interconnections, for example, switches, Network Interfaces and connections. We focus on the system connections to decrease the power scattering. There are numerous strategies makes utilization of protecting and line to line dispersing. The proficient approach to decrease the power is Data Encoding Techniques with Pre-calculation rationale which diminishes the exchanging action and coupling exchanging movement. Transport transform strategy can be utilized to encode the scattered information designs arbitrarily. A few procedures have been proposed in the writing to decrease the power dispersed by the connections of NoC [3]. Wormhole exchanging is the most legitimate decision for on-chip communication [2]. The coupling driven transport transform strategy is proposed to handle the coupling power lessening issue.

A set of data encoding schemes are utilized to reduce the power dissipated by the link so far Network on Chip utilizing a pre-calculation rationale. One of the best power buyers in a framework is exchanging movement on the exceedingly capacitive lines of an interconnection system [4]. Self switching activity and couplings witching activity are reliable for link power dissipation. The fundamental objective of this approach is to lessen the exchanging movement and coupling exchanging action and the technique utilized is to encode the dances before they are infused into the system. The power dispersed by indicates point interface association can be decreased by encoding the active flutter barring the header dance. Coupling moves comprises of four distinct sorts. In Type I move, one line switches where another stay unaffected. A Type II move happens when one changes from high to low or the other way around. Sort III move happens when both lines switches in the meantime. Sort IV moves has both the lines don't switch and stays unaltered. By changing over the Type moves the exchanging action can be limited. There are three plans used to lessen the power. They are odd encoding plans, odd and full encoding plans. The Encoder design is same for all plans yet the inward piece of encoder differs relating to its plan.

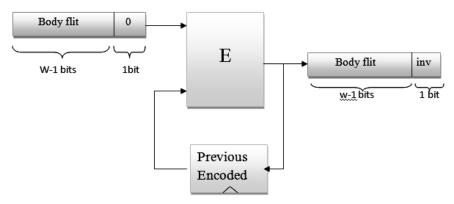

Figure 1: Data encoder architecture

#### 2.1. Odd Encoding Scheme

In this plan Type I moves are decreased and changed over to diminish the exchanging action. The present information is contrasted with the past one with check for odd reversal.

The information is given to the sort changes where it comprises of Ty piece and every square takes two neighboring bits in the info. The information comprises of *w* bits where *w*-1 it's are given as info and 1 bit is utilized to show the reversal. In the event that any moves are made it is identified and thought about in the pre-calculation logic. Pre-calculation is a proposed rationale enhancement procedure which specifically disables

the contributions of a consecutive rationale circuit, consequently diminishing exchanging action and power dissemination, without changing rationale functionality [6]. The transitions are tallied and relying upon the check the reversal can be performed in odd bits.

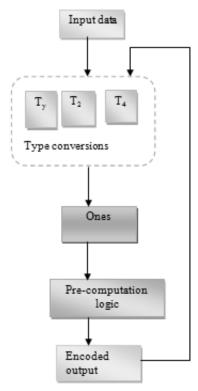

Figure 2: Encoder obstruct for odd encoding plan

#### 2.2. Odd And Full Encoding Scheme

Here, Type II move is changed over into Type IV moves to lessen the power. The sources of info are offered like the past plan. The T2 and T4\*\* are incorporated into the sort changes to undercover the sort moves. At that point the ones square include the quantity of ones the information and is given to pre-calculation rationale where the correlation is made a little bit at a time and chooses for odd or full reversal so the encoding is made odd or full bits correspondingly to diminish the exchanging action and coupling exchanging movement.

# 3. RESULTS AND DISCUSSION

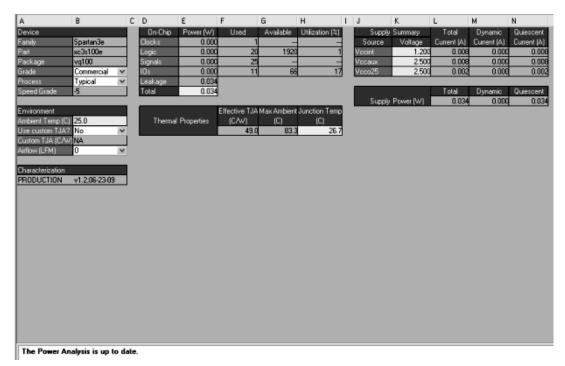

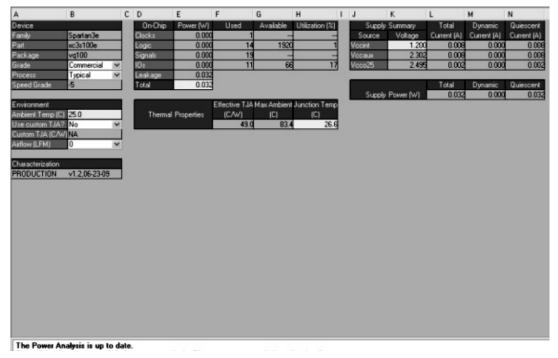

The projects are composed in Verilog and reproduced in the Xilinx 13.2 instrument. The sources of info are given in 4bits and confirmed with the ISim test system in Xilinx. The power is measured utilizing the power analyzer in a similar apparatus.

Figure 4: (a) The power calculation of scheme I in [5] (0.034W)

Figure 4: (b) The power calculation of odd and encoding scheme in [5] (0.034W)

## 4. CONCLUSION

In this paper a Novel Data Encoding Technique is introduced to decrease the power in system joins. The connections are in charge of a critical division of general power disseminated by the correspondence framework. The Pre-Computation technique is utilized to stay away from the rehashed calculation which decreases the exchanging action that diminishes the power. The proposed procedure is to limit the exchanging movement as well as the coupling exchanging action which is basically in charge of connection power dissemination. There are three plans in this Encoding technique. At long last, the power can be decreased with this strategy contrasted with the conventional technique. The power has been broke down utilizing the test system and contrasted and the current strategies.

#### REFERENCES

- [1] Dhivya R, Kavitha V, Secured Client Cache Sustain for Maintaining Consistency in MANET's, International Journal of Research in Engineering and Technology, 3 (7), 2014, 1-6.

- [2] Gayathri C, Kavitha V, Mitigation of Colluding Selective Forwarding Attack in WMN's using FADE, International Journal for Trends in Engineering and Technology, 3 (1), 2015, 6-12.

- [3] Kavitha V, Veeralakshmi C, Surveillance on Many casting Over Optical Burst Switching Networks under Secure Sparse Regeneration, Journal of Electronics and Communication Engineering, 4 (6), 2013, 1-8.

- [4] Huang.Z.Y and Tsai.T.Y, Efficient implementation of QR decompo-sition for gigabit MIMO-OFDM systems, IEEE Trans. Circuits Syst. I, Reg. Papers, 58(10), 2011, 2531-2542

- [5] Mohammed.K, Mohamed.M.I.A, and Daneshrad.B, A parameterized programmable MIMO decoding architecture with a scalable instruction set and compiler, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 19(8), 2011, 1485-1489

- [6] Karim Mohammed, A Parameterized Programmable MIMO Decoding Architecture With a Scalable Instruction Set and Compiler, IEEE Transactions On Very Large Scale Integration (VISI) Systems, 18(11), 2010.

- [7] M. Palesi, G. Ascia, F. Fazzino, and V. Catania, "Data encoding schemes in networks on chip," *IEEE Trans. Computer.-Aided Design Integr. Circuits Syst.*, Vol. 30, No. 5, pp. 774-786, May 2011.

- [8] "Public Control Algorithm for a Multi Access Scenario comparsing GPRS and UMTS ", at Department of Computer Science and Engineering, National Conference on "Intelligent computing With IoT on April 16 2016 in Dhirajlal Gandhi College of Technology.

- [9] "Teleimersion" Research Journal of Pharmaceutical, Biological and Chemical Sciences on March April 2016 issue. (Impact Factor 0.35Indexed in Scopus). http://www.rjpbcs.com/pdf/2016\_7(2)/%5b131%5d.pdf

- [10] NimaJafarzadeh, Maurizio Palesi, and Ali Afzali-Kusha, "Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chip," *IEEE Tran. Very Large Scale Integr. (VLSI) Syst.vol.*22, no.3, pp.675-685, Mar 2014.